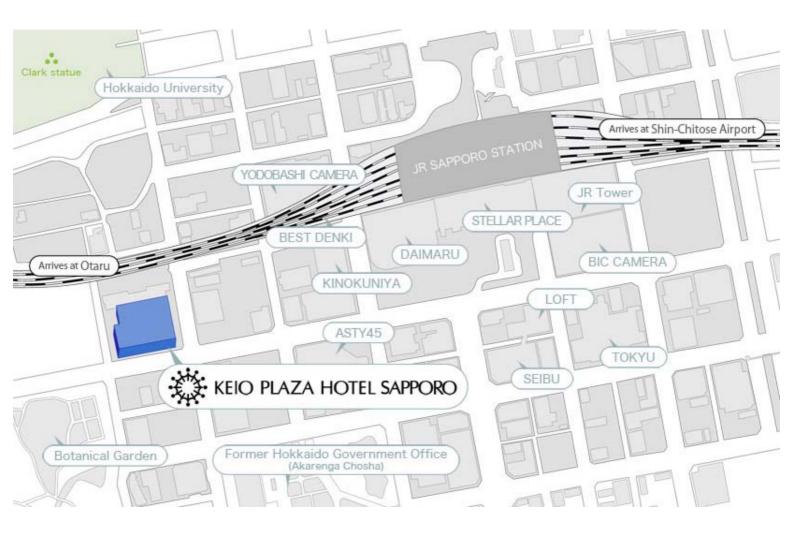

The Seventeenth Asian Test Symposium November 24-27, 2008, Keio Plaza Hotel Sapporo, Sapporo, JAPAN

Message to attendants of ATS 2008 from local arrangement chairs.

#### **General Information**

- Sponsors/Supporters

- Scope

- Key Dates

- More Information

#### **Registration**

- Early Registration Registration Form [pdf/doc]

- VISA Guide

#### ATS'08 Program

- ATS'08 at a glance

- Advance Program

- **Tutorials**

- Keynote Speech/ .

- Invited Talk

- Social Program

#### **Accommodations**

- Hotel Reservation Guide (at Keio Plaza Hotel Sapporo)

- Alternative Hotels

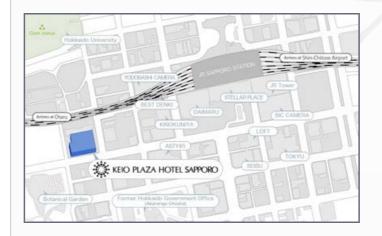

#### **Conference Location**

- The Venue

- <u>Access</u>

- Sapporo Convention Bureau

- Sapporo White Illumination (in Japanese)

- Message from local arrangement chairs

#### Call for Papers

• PDF version

#### Paper Submission

- Regular Session <u>To WelCoMe system</u> (paper submission)

- Industrial Session

#### **Committees**

- Organizing Committee

- Program Committee

#### **Related Links**

WRTLT'08 (In conjunction with

#### **General Information**

#### **SPONSORS**

- IEEE Computer Society, Test Technology Technical Council

- The IEICE Information and Systems Society, Technical Committee on DC

- <u>Kyushu Institute of Technology</u>

#### **SUPPORTERS**

#### **SCOPE**

The Asian Test Symposium (ATS) provides an international forum for engineers and researchers from all countries of the world, especially from Asia, to present and discuss various aspects of device, board and system testing with design, manufacturing and field considerations in mind. The official language of the symposium is English.

Topics of interest include, but are not limited to:

- Automatic Test Generation / Fault Simulation

- Design for Testability / Synthesis for Testability

- Built-In Self-Test / Test Data Compression •

- **Delay Testing** ٠

- Defect-Based Testing / IDDX Testing

- Power Issues in Test •

- •

- •

- Fault Modeling & Diagnosis Memory Test / FPGA Test Analog and Mixed-Signal Test

- RF Testing / High-Speed I/O Test

- System-on-a-Chip Test

- Board and System Test • Network Protocol Testing •

- Design Verification and Validation •

- **On-Line** Test

- Fault Tolerance / Dependable System •

- Software Testing / Software Design for Testing

- Economics of Test

#### **KEY DATES**

| The Seventeenth Asian Test Symposium (ATS 2008) |                                                                                                                      |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| <u>ATS'08)</u>                                  | Ealry Registration: Oct. 24th, 2008.                                                                                 |

|                                                 |                                                                                                                      |

|                                                 | MORE INFORMATION                                                                                                     |

|                                                 | For general information<br>General Co-Chairs: Yasuo Sato and Seiji Kajihara<br>(ats08-gc@dsgn.im.hiroshima-cu.ac.jp) |

|                                                 | For submission related information<br>Program Chair: Kazumi Hatayama<br>(ats08-pc@dsgn.im.hiroshima-cu.ac.jp)        |

|                                                 | For industry session information<br>Industry Chair: Toshinobu Ono<br>(ats08-ic@dsgn.im.hiroshima-cu.ac.jp)           |

|                                                 |                                                                                                                      |

| A                                               | TS 2008 Organizing Committee   ats08.info.hiroshima-cu.ac.jp                                                         |

The Seventeenth Asian Test Symposium November 24-27, 2008, Keio Plaza Hotel Sapporo, Sapporo, JAPAN

Message to attendants of ATS 2008 from local arrangement chairs.

#### **General Information**

- <u>Sponsors/Supporters</u>

- <u>Scope</u>

- <u>Key Dates</u>

- More Information

#### **Registration**

- Early Registration

Registration Form

[pdf/doc]

- <u>VISA Guide</u>

#### ATS'08 Program

- ATS'08 at a glance

- Advance Program

- <u>Tutorials</u>

- Keynote Speech/

- Invited Talk

- <u>Social Program</u>

#### **Accommodations**

- Hotel Reservation Guide

(at Keio Plaza Hotel

Sapporo)

- <u>Alternative Hotels</u>

#### **Conference Location**

- The Venue

- <u>Access</u>

- <u>Sapporo Convention</u>

<u>Bureau</u>

- <u>Sapporo White Illumination</u>

<u>(in Japanese)</u>

- <u>Message from local</u> <u>arrangement chairs</u>

#### **Call for Papers**

<u>PDF version</u>

#### Paper Submission

- <u>Regular Session</u>

<u>To WelCoMe system</u>

- (paper submission) • Industrial Session

#### Committees

- Organizing Committee

- <u>Program Committee</u>

#### **Related Links**

WRTLT'08 (In conjunction with)

#### Message to attendants of ATS 2008 from local arrangement chairs

Sapporo has already become winter from autumn season since Nov.4. Now, it is snow and cold in Sapporo. The maximum temperature will be 5 centigrade and the minimum one will be -2 centigrade in your stay.

When you walk along the outside of a building, the followings are required: a coat, a muffler, a glove and an umbrella. Boots may not be necessary, but shoes with a thick bottom are suitable for walking around in Sapporo. You can buy them in the Chitose airport and in department stores inside the Sapporo station. Please visit to the following web page introducing <u>Climate and Clothes in Sapporo</u>.

On the other hand, it is comfortable in the ATS08 conference site, Keio Plaza Hotel Sapporo, since good air conditioners work. You will be able to spend with a thin sweater inside the hotel. If you wear thick dress in the conference site, you will feel that it is very hot. We recommend you to bring a thin sweater for spending in the conference site.

We hope to see you in Sapporo, soon.

H. Yotsuyanagi and M. Hashizume, Local Arrangement Chairs

The Seventeenth Asian Test Symposium (ATS 2008)

<u>ATS'08)</u>

The Seventeenth Asian Test Symposium November 24-27, 2008, Keio Plaza Hotel Sapporo, Sapporo, JAPAN

Message to attendants of ATS 2008 from local arrangement chairs.

#### **General Information**

- Sponsors/Supporters

- Scope

- Key Dates

- More Information

#### **Registration**

- Early Registration Registration Form [pdf/doc]

- VISA Guide

#### ATS'08 Program

- ATS'08 at a glance

- Advance Program

- **Tutorials**

- Keynote Speech/ .

- Invited Talk

- Social Program

#### **Accommodations**

- Hotel Reservation Guide (at Keio Plaza Hotel Sapporo)

- Alternative Hotels

#### **Conference Location**

- The Venue

- <u>Access</u>

- Sapporo Convention Bureau

- Sapporo White Illumination (in Japanese)

- Message from local arrangement chairs

#### Call for Papers

• PDF version

#### Paper Submission

- Regular Session <u>To WelCoMe system</u> (paper submission)

- Industrial Session

#### **Committees**

- Organizing Committee

- Program Committee

#### **Related Links**

WRTLT'08 (In conjunction with

#### **General Information**

#### **SPONSORS**

- IEEE Computer Society, Test Technology Technical Council

- The IEICE Information and Systems Society, Technical Committee on DC

- <u>Kyushu Institute of Technology</u>

#### **SUPPORTERS**

#### **SCOPE**

The Asian Test Symposium (ATS) provides an international forum for engineers and researchers from all countries of the world, especially from Asia, to present and discuss various aspects of device, board and system testing with design, manufacturing and field considerations in mind. The official language of the symposium is English.

Topics of interest include, but are not limited to:

- Automatic Test Generation / Fault Simulation

- Design for Testability / Synthesis for Testability

- Built-In Self-Test / Test Data Compression •

- **Delay Testing** ٠

- Defect-Based Testing / IDDX Testing

- Power Issues in Test •

- •

- •

- Fault Modeling & Diagnosis Memory Test / FPGA Test Analog and Mixed-Signal Test

- RF Testing / High-Speed I/O Test

- System-on-a-Chip Test

- Board and System Test • Network Protocol Testing •

- Design Verification and Validation •

- **On-Line** Test

- Fault Tolerance / Dependable System •

- Software Testing / Software Design for Testing

- Economics of Test

#### **KEY DATES**

| The Seventeenth Asian Test Symposium (ATS 2008) |                                                                                                                                                            |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>ATS'08)</u>                                  | Ealry Registration: Oct. 24th, 2008.                                                                                                                       |

|                                                 |                                                                                                                                                            |

|                                                 | MORE INFORMATION                                                                                                                                           |

|                                                 | For general information<br>General Co-Chairs: Yasuo Sato and Seiji Kajihara<br>(ats08-gc@dsgn.im.hiroshima-cu.ac.jp)<br>For submission related information |

|                                                 | Program Chair: Kazumi Hatayama<br>(ats08-pc@dsgn.im.hiroshima-cu.ac.jp)                                                                                    |

|                                                 | For industry session information<br>Industry Chair: Toshinobu Ono<br>(ats08-ic@dsgn.im.hiroshima-cu.ac.jp)                                                 |

|                                                 |                                                                                                                                                            |

| TA                                              | TS 2008 Organizing Committee   ats08.info.hiroshima-cu.ac.jp                                                                                               |

The Seventeenth Asian Test Symposium November 24-27, 2008, <u>Keio Plaza Hotel Sapporo</u>, Sapporo, JAPAN

News: Ealry Registration closes on Oct. 24th, 2008.

#### **General Information**

- <u>Sponsors/Supporters</u>

- <u>Scope</u>

- <u>Key Dates</u>

- More Information

#### **Registration**

- Early Registration

Registration Form

[pdf/doc]

- <u>VISA Guide</u>

#### ATS'08 Program

- ATS'08 at a glance

- <u>Advance Program</u>

- <u>Tutorials</u>

- Keynote Speech/

- Invited Talk

- <u>Social Program</u>

#### Accommodations

- Hotel Reservation Guide (at Keio Plaza Hotel Sapporo)

- <u>Alternative Hotels</u>

#### **Conference Location**

- The Venue

- <u>Access</u>

- <u>Sapporo Convention</u>

<u>Bureau</u>

- <u>Sapporo White Illumination</u>

<u>(in Japanese)</u>

#### Call for Papers

PDF version

#### Paper Submission

- <u>Regular Session</u>

<u>To WelCoMe system</u> (paper submission)

- Industrial Session

#### Committees

- Organizing Committee

- Program Committee

- **Related Links**

- <u>WRTLT'08</u> (<u>In conjunction with</u> ATS'08)

#### Registration

Early Registration (until Oct. 24th, 2008)

Please fill out a registration form and E-MAIL or FAX or Mail to ATS'08 Registration Chair by October 24th.

Prof. Toshinori Hosokawa (ATS'08 Registration Chair) E-mail: t7hosoka@cit.nihon-u.ac.jp Fax: +81-47-474-2669 Mail Address: Dept. of Mathematical Information Eng., College of Industrial Technology, Nihon University, 1-2-1, Izumicho, Narashino, Chiba 275-8575, Japan

To download Registration Forms, click here for PDF, and here for Word.

Important Note:

- At least one author must register with the paper reference number by August 11.

- No registration form will be accepted after November 14. After November 14, please register at the symposium. Only the cash in Japanese Yen will be acceptable at the on-site registration desk.

- Participant lists including name, affiliation, and country will be distributed to attendees.

- REFUND POLICY: All refund requests must be in writing and received by 24 October 2008 will be reimbursed minus a 5,000 yen administrative fee. No refunds will be issued after 24 October.

#### Registration Fees:

|                                                     |                                                    |                  | Tutorial         |                  |                           |                  |

|-----------------------------------------------------|----------------------------------------------------|------------------|------------------|------------------|---------------------------|------------------|

| Registration fees<br>(Japanese Yen)                 | Symposium                                          |                  | Tutoria<br>Tuto  |                  | Tutorial1 OR<br>Turorial2 |                  |

|                                                     | Until<br>Oct. 24                                   | After<br>Oct. 24 | Until<br>Oct. 24 | After<br>Oct. 24 | Until<br>Oct. 24          | After<br>Oct. 24 |

| IEEE member *1, 3                                   | 45,000                                             | 54,000           | 26,000           | 33,000           | 16,000                    | 20,000           |

| Non-member *3                                       | 57,000                                             | 69,000           | 36,000           | 45,000           | 21,000                    | 27,000           |

| IEEE student<br>member *1, 3                        | 11,000                                             | 13,000           | 16,000           | 20,000           | 16,000                    | 20,000           |

| Student non-<br>member                              | 14,000                                             | 17,000           | 16,000           | 20,000           | 16,000                    | 20,000           |

| Extra pages *2,4                                    | 10,000 each page(at most 2 for each regular paper) |                  |                  |                  |                           |                  |

| Extra social event<br>tickets                       | 10,000 each ticket                                 |                  |                  |                  |                           |                  |

| IFFF member rate is also applied for IFICF members. |                                                    |                  |                  |                  |                           |                  |

IEEE member rate is also applied for IEICE members. Extra pages fee for each paper more than 6 pages must be paid by August 11. Please indicate the paper reference number above. Registration fee for IEEE member and Non-member includes social event tickets.

|                                                               | Student fees do not include the social event (the reception, the tour and the banquet).<br>Only regular papers can apply for extra pages.                                                                                                                                                                                                                                                                                                                               |  |  |  |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                               | Payment Methods:                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                                                               | <ul> <li>Bank transfer<br/>(日本国内からはこちらをお選び下さい.振込手数料はご本人で負担願います.)</li> <li>Bank Name: The Bank of Tokyo-Mitsubishi UFJ Branch name: Tama Center Branch<br/>Account Number: 2217251</li> <li>Account Name: ATS Finance kaikei Miura Yukiya         <ul> <li>Any handling fees for the bank transfer would be borne by you.</li> </ul> </li> <li>Credit card(VISA or MASTER) Overseas Only.<br/>Sending the card number by FAX or MAIL is strongly recommended.</li> </ul> |  |  |  |

| ATS 2008 Organizing Committee   ats08.info.hiroshima-cu.ac.jp |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

### The Seventeenth Asian Test Symposium

http://ats08.info.hiroshima-cu.ac.jp/ Keio Plaza Hotel Sapporo, Sapporo, JAPAN November 24-27, 2008

### **Registration Form**

E-MAIL or FAX or Mail this form to: Toshinori Hosokawa, ATS'08 Registration Chair

E-mail: <u>t7hosoka@cit.nihon-u.ac.jp</u> Fax: +81-47-474-2669

Mail Address: Dept. of Mathematical Information Eng., College of IndustrialTechnology, Nihon University, 1-2-1, Izumicho, Narashino, Chiba 275-8575, Japan

Please TYPE or print BLOCK LETTERS. Fill out one form per participant. For early registration, send it back by October 24. At least one author must register with the paper reference number by August 11. No registration form will be accepted after November 14. After November 14, please register at the symposium. Participant lists including name, affiliation, and country will be distributed to attendees.

| Name: (Last)         |                   | (First) | (Middle) |  |

|----------------------|-------------------|---------|----------|--|

| Affiliation/company: |                   |         |          |  |

| Mailing address:     |                   |         |          |  |

| (Zip/Postal code)    | Tel:<br>(Country) | Fax:    | E-mail:  |  |

IEEE membership number: \_\_\_\_\_ Paper reference number (only for authors): \_\_\_\_\_ IEICE membership number: \_\_\_\_\_

|                                       |                |       |                | Tutorial       |                 |                           |               |                           |  |          |

|---------------------------------------|----------------|-------|----------------|----------------|-----------------|---------------------------|---------------|---------------------------|--|----------|

| Registration fees<br>( Japanese Yen)  | Symp           |       | Sym            |                | oosium          | Tutorial 1 and Tutorial 2 |               | Tutorial1 or<br>Turorial2 |  | Subtotal |

|                                       | Until Oct      | t. 24 | After Oct. 24  | Until Oct. 24  | After Oct. 24   | Until Oct. 24             | After Oct. 24 |                           |  |          |

| IEEE member* <sup>1, *3</sup>         | <b>4</b> 5,0   | 00    | □ 54,000       | 26,000         | <b>3</b> 3,000  | <b>1</b> 6,000            | 20,000        |                           |  |          |

| Non-member <sup>*3</sup>              | <b>5</b> 7,0   | 00    | □ 69,000       | <b>3</b> 6,000 | <b>4</b> 5,000  | <b>1</b> 21,000           | 27,000        |                           |  |          |

| IEEE student member* <sup>1, *3</sup> | <b>11,0</b>    | 00    | <b>1</b> 3,000 | <b>1</b> 6,000 | 20,000          | <b>1</b> 6,000            | 20,000        |                           |  |          |

| Student non-member*3                  | <b>1</b> 4,0   | 00    | <b>1</b> 7,000 | <b>1</b> 6,000 | <b>D</b> 20,000 | <b>1</b> 6,000            | 20,000        |                           |  |          |

| Extra pages fees*2,*4                 | □10,000 each X |       |                | extra pag      | e(s) (at most 2 | for each regu             | lar paper)    |                           |  |          |

| Extra social event tickets            | □10,000 each X |       |                | ticket(s)      |                 |                           |               |                           |  |          |

| Total                                 |                |       |                |                |                 |                           |               |                           |  |          |

\*<sup>1</sup> IEEE member rate is also applied for IEICE members.

administrative fee. No refunds will be issued after 24 October.

\*<sup>2</sup> Extra pages fee for each paper more than 6 pages must be paid by August 11. Please indicate the paper reference number above.

\*<sup>3</sup> Registration fee for IEEE member and Non-member includes social event tickets. Student fees do not include the social event (the reception, the tour and the banquet).

\*<sup>4</sup> Only regular papers can apply for extra pages.

| Payment method: (日本国内からは銀行振込にてお                                                                            | 支払い下さい。振込手              | 数料はご負担下さ             | さい。)                   |

|------------------------------------------------------------------------------------------------------------|-------------------------|----------------------|------------------------|

| Bank transfer (Any handling fees for the bank transfer                                                     |                         |                      |                        |

| I will remit / have remitted the fee on                                                                    |                         |                      |                        |

| (Date)                                                                                                     |                         | (Name of remitter)   |                        |

| Bank Name: The Bank of Tokyo-Mitsubishi UFJ                                                                | Branch name: Ta         | ma Center Branch     |                        |

| Account Number: 2217251                                                                                    |                         |                      |                        |

| Account Name: ATS Finance kaikei Miura Yukiya                                                              |                         |                      |                        |

| (銀行:三菱東京UFJ銀行 支店:多摩センター                                                                                    | 口座:(普通)2217251          | 名義:ATS Finance       | カイケイ ミウラユキャ            |

| ATMでの振り込みの場合の名義:「ATS」 また                                                                                   | は「エーテイーエス」)             |                      |                        |

| Credit card (Overseas only. Sending the card number<br>I pay the fee to one of the following credit cards: |                         |                      |                        |

| Card number:                                                                                               | Expir                   | ation date: /        | (Month/year)           |

| Card holder:                                                                                               |                         |                      |                        |

| (Type or print block letters)                                                                              |                         |                      |                        |

| Signature of the card holder:                                                                              |                         | Date:                |                        |

| REFUND POLICY: All refund requests must be in writing                                                      | and received by 24 Octo | ber 2008 will be rei | mbursed minus a ¥5.000 |

The Seventeenth Asian Test Symposium November 24-27, 2008, <u>Keio Plaza Hotel Sapporo</u>, Sapporo, JAPAN

News: Ealry Registration closes on Oct. 24th, 2008.

#### **General Information**

- <u>Sponsors/Supporters</u>

- <u>Scope</u>

- <u>Key Dates</u>

- More Information

#### **Registration**

- Early Registration

Registration Form

[pdf/doc]

- <u>VISA Guide</u>

#### ATS'08 Program

- ATS'08 at a glance

- Advance Program

- <u>Tutorials</u>

- Keynote Speech/

- Invited Talk

- <u>Social Program</u>

#### **Accommodations**

- Hotel Reservation Guide

(at Keio Plaza Hotel

Sapporo)

- <u>Alternative Hotels</u>

#### **Conference Location**

- The Venue

- <u>Access</u>

- <u>Sapporo Convention</u>

<u>Bureau</u>

- <u>Sapporo White Illumination</u>

<u>(in Japanese)</u>

#### Call for Papers

PDF version

#### Paper Submission

- <u>Regular Session</u>

<u>To WelCoMe system</u> (paper submission)

- Industrial Session

#### Committees

- Organizing Committee

- Program Committee

#### **Related Links**

<u>WRTLT'08</u> (<u>In conjunction with</u> ATS'08)

#### Registration

#### Visa Guide

ATS'08 Organizing Committee will send visa letters (confirmation letters) to individuals requesting them. Please fill <u>the request form</u> and send it to Registration Chair (e-mail: ats08-rc@dsgn.im.hiroshima-cu.ac.jp) if you request visa letters.

Download the request form for visa letter

Visa letters will only be issued to:

- Speakers / Presenters,

- Committee Members,

- Attendees who have paid their registration fee in full.

Mailing visa letters often takes two or three weeks. Please request them well in advance.

Basic information about visa application can be found on the web site of The Ministry of Foreign Affairs of Japan: <u>http://www.mofa.go.jp/j\_info/visit/visa/index.html</u>.

Please contact <u>the diplomatic mission</u> nearest you if you need the details about your visa application.

• For Chinese attendees, detailed information is provided on the web site of Embassy of Japan in China.

The Seventeenth Asian Test Symposium November 24-27, 2008, <u>Keio Plaza Hotel Sapporo</u>, Sapporo, JAPAN

News: Ealry Registration closes on Oct. 24th, 2008.

and Dependable System

|                 | 9:00-           |                                                                     | Tutorial 1                                               |                                               |  |  |  |  |

|-----------------|-----------------|---------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------|--|--|--|--|

| 11/24           | 12:00<br>13:30- |                                                                     |                                                          |                                               |  |  |  |  |

| (Mon.)          |                 |                                                                     | Tutorial 2                                               |                                               |  |  |  |  |

|                 | 18:00-<br>20:00 |                                                                     | <u>Welcome</u><br><u>Reception</u>                       |                                               |  |  |  |  |

|                 | 9:00-<br>10:15  |                                                                     | Plenary Session 1                                        |                                               |  |  |  |  |

|                 | 10:15-<br>10:45 |                                                                     | Coffee Break                                             |                                               |  |  |  |  |

|                 | 10:45-<br>12:00 |                                                                     | Plenary Session 2                                        |                                               |  |  |  |  |

|                 | 12:00-<br>13:30 |                                                                     | Lunch Time                                               |                                               |  |  |  |  |

| 11/25<br>(Tue.) | 13:30-<br>14:45 | <u>3A: Test Data &amp;</u><br><u>Response</u><br><u>Compression</u> | 3B: Test Generation<br>and Fault Simulation              | <u>3C: RF Testing</u>                         |  |  |  |  |

|                 | 14:45-<br>15:15 | Coffee Break                                                        |                                                          |                                               |  |  |  |  |

|                 | 15:15-<br>16:30 | <u>4A: Test</u><br>Compression and<br>BIST                          | <u>4B: Test Generation</u><br><u>for Physical Faults</u> | 4C: Analog and Mixed<br>Signal Test           |  |  |  |  |

|                 | 17:00-<br>20:30 | Social Event (Sapporo Beer Garden)                                  |                                                          |                                               |  |  |  |  |

|                 | 9:00-<br>10:15  | 5A: Delay Testing                                                   | 5B: Analog Production<br>Test 1                          | 5C: Hybrid Method fo<br>Test Data Compression |  |  |  |  |

|                 | 10:15-<br>10:45 | Coffee Break                                                        |                                                          |                                               |  |  |  |  |

|                 | 10:45-<br>12:00 | 6A: Fault Diagnosis                                                 | 6B: Analog Production<br>Test 2                          | <u>6C: Defect Based</u><br><u>Testing</u>     |  |  |  |  |

|                 | 12:00-<br>13:30 | Lunch Time                                                          |                                                          |                                               |  |  |  |  |

| 11/26<br>(Wed.) |                 | 7A: Panel Session                                                   | 7B: Power Aware Test<br>Generation                       | 7C: Design for Efficie<br>Test                |  |  |  |  |

|                 | 14:45-<br>15:15 |                                                                     | Coffee Break                                             |                                               |  |  |  |  |

|                 | 15:15-<br>17:00 | 8A: Industry Session                                                | 8B: SoC Test                                             | 8C: Design Verification<br>and Validation     |  |  |  |  |

|                 | 17:00-<br>17:45 |                                                                     | Poster Session (Foye                                     | )                                             |  |  |  |  |

|                 | 18:00-<br>20:00 |                                                                     | Banquet                                                  |                                               |  |  |  |  |

|                 | 9:00-<br>10:15  | 9A: Power Aware<br>Scan Test                                        | 9B: Memory Self Test                                     | 9C: On-Line Test                              |  |  |  |  |

|                 | 10:15-<br>10:45 |                                                                     | Coffee Break                                             |                                               |  |  |  |  |

|                 | 10:45-          | 10A: Power Aware                                                    | 10B: Advanced                                            | 10C: Fault Tolerance                          |  |  |  |  |

Memory Test

#### **General Information**

- Sponsors/Supporters

- <u>Scope</u>

- <u>Key Dates</u>

- More Information

#### **Registration**

Early Registration

Registration Form

[pdf/doc]

### <u>VISA Guide</u>

#### ATS'08 Program

- ATS'08 at a glance

- <u>Advance Program</u>

- <u>Tutorials</u>

- Keynote Speech/

- Invited Talk

- Social Program

#### **Accommodations**

- Hotel Reservation Guide

(at Keio Plaza Hotel

Sapporo)

- <u>Alternative Hotels</u>

#### **Conference Location**

- The Venue

- <u>Access</u>

- <u>Sapporo Convention</u>

<u>Bureau</u>

- <u>Sapporo White Illumination</u> (in Japanese)

#### **Call for Papers**

PDF version

#### Paper Submission

- <u>Regular Session</u>

<u>To WelCoMe system</u> (paper submission)

- Industrial Session

#### Committees

- Organizing Committee

- Program Committee

#### **Related Links**

<u>WRTLT'08</u> (<u>In conjunction with</u> <u>ATS'08</u>)

12:00

Delay Testing

The Seventeenth Asian Test Symposium November 24-27, 2008, <u>Keio Plaza Hotel Sapporo</u>, Sapporo, JAPAN

News: Ealry Registration closes on Oct. 24th, 2008.

#### **General Information**

- Sponsors/Supporters

- <u>Scope</u>

- <u>Key Dates</u>

- More Information

#### **Registration**

- Early Registration

Registration Form

[pdf/doc]

- <u>VISA Guide</u>

#### ATS'08 Program

- ATS'08 at a glance

- <u>Advance Program</u>

- <u>Tutorials</u>

- <u>Keynote Speech/</u> Invited Talk

- Social Program

#### **Accommodations**

- Hotel Reservation Guide

(at Keio Plaza Hotel

Sapporo)

- <u>Alternative Hotels</u>

#### **Conference Location**

- <u>The Venue</u>

- <u>Access</u>

- <u>Sapporo Convention</u>

<u>Bureau</u>

- <u>Sapporo White Illumination</u>

<u>(in Japanese)</u>

#### Call for Papers

PDF version

#### Paper Submission

- <u>Regular Session</u>

<u>To WelCoMe system</u> (paper submission)

- Industrial Session

#### Committees

- Organizing Committee

- Program Committee

#### **Related Links**

<u>WRTLT'08</u> (<u>In conjunction with</u> <u>ATS'08)</u>

#### Advance Program

Jump to 24th, 25th, 26th, 27th

#### Nov 24th, 2008

9:00-12:00 <u>Tutorial 1</u> <u>Statistical Screening Methods Targeting "Zero Defect" IC Quality and Reliability</u>

13:30- 16:30 <u>Tutorial 2</u> Delay Testing: Theory and Practice

#### Nov 25th, 2008

9:00-10:10 Plenary Session 1

#### 9:00-9:20 Opening Remarks

<u>9:20-9:45 Keynote Speech 1</u> <u>The Value of Extending Test Solutions</u> <u>Brian STEVENS (National Semiconductor - USA)</u>

<u>9:45-10:10 Keynote Speech 2</u> <u>Architectural Evolution and Test Requirements in Digital-Convergence Era</u> <u>Kunio UCHIYAMA (Hitachi - Japan)</u>

#### 10:40-12:00 Plenary Session 2

<u>10:40-11:20 Invited Talk 1</u> <u>The role of DFT in Yield</u> <u>Brady BENWARE (Mentor Graphics - USA)</u>

<u>11:20-12:00 Invited Talk 2</u> <u>Issues and new Scenario for Deep sub-micron LSI design and Testing</u> <u>Kunihiro ASADA (Univ. of Tokyo - Japan)</u>

#### 13:00-14:15 Session 3A: Test Data & Response Compression

Not All Xs are Bad for Scan Compression Anshuman CHANDRA, Rohit KAPUR (Synopsys - USA)

Evaluation of Entropy Driven Compression Bounds on Industrial Designs

Srinivasuiu ALAMPALLY (TI - India), Jais ABRAHAM (AMD - India), Rubin A. PAREKHJI (TI - India), Rohit KAPUR, T. W. WILLIAMS (Synopsys - USA)

#### 13:00-14:15 Session 3B: Test Generation and Fault Simulation

Untestable Fault Identification in Sequential Circuits Using Model-Checking Jaan RAIK (Tallinn Univ. of Tech. - Estonia), Hideo FUJIWARA (NAIST - Japan), Raimund UBAR, Anna KRIVENKO (Tallinn Univ. of Tech. - Estonia)

A Test Generation Method for State-Observable FSMs to Increase Defect Coverage under the Test Length Constraint Ryoichi INOUE, Toshinori HOSOKAWA (Nihon Univ. - Japan), Hideo FUJIWARA (NAIST - Japan)

LIFTING: a Flexible Open-Source Fault Simulator Alberto BOSIO, Giorgio DI NATALE (LIRMM - France)

#### 13:00-14:15 Session 3C: RF Testing

Digitally-Assisted Analog/RF Testing for Mixed-Signal SoCs Hsiu-Ming CHANG (UCSB - USA), Min-Sheng LIN (Broadcom - USA), Kwang-Ting CHENG (UCSB - USA)

Low-Cost One-Port Approach for Testing Integrated RF Substrates Abhilash GOYAL, Madhavan SWAMINATHAN (Georgia Tech. - USA)

Efficient Low-Cost Testing of Wireless OFDM Polar Transceiver Systems Deuk LEE, Vishwanath NATARAJAN, R. SENGUTTUVAN, Abhijit CHATTERJEE (Georgia Tech. - USA)

#### 15:15-16:30 Session 4A: Test Compression and BIST

Interconnect-Driven Layout-Aware Multiple Scan Tree Synthesis for Test Time, Data Compression and Routing Optimization Katherine Shu-Min L, Jr-Yang HUANG (National Sun Yat-Sen Univ. - Taiwan)

Sequential Circuit BIST Synthesis using Spectrum and Noise from ATPG Patterns Nitin YOGI, Vishwani D. AGRAWAL (Auburn Univ. - USA)

A Novel BIST Scheme Using Test Vectors Applied by Circuit-under-Test Itself Jishun KUANG, Xiong OUYANG, Zhiqiang YOU (Hunan Univ. - China)

#### 15:15-16:30 Session 4B: Test Generation for Physical Faults

XPDF-ATPG: An Efficient Test Pattern Generation for Crosstalk-Induced Faults Sunghoon CHUN, Yongjoon KIM, Taejin KIM, Myung-Hoon YANG, Sungho KANG (Yonsei Univ. - Korea)

A Multi-Valued Algebra for Capacitance Induced Crosstalk Delay Faults Arani SINHA (AMD - USA), Sandeep GUPTA, Melvin BREUER (USC - USA)

Increasing Defect Coverage by Generating Test Vectors for Stuck-open Faults Yoshinobu HIGAMI (Ehime Univ.- Japan), Kewal K. SALUJA (Univ. of Wisconsin-Madison - USA), Hiroshi TAKAHASHI, Shin-ya KOBAYASHI, Yuzo TAKAMATSU (Ehime Univ. - Japan)

15:15-16:30 Session 4C: Analog and Mixed-Signal Test

Technique to Improve the Performance of Time-Interleaved A-D Converters with

| Mismatches of Non-Iinearity<br>Koji ASAMI (Advantest - Japan), Hidetaka SUZUKI, Hiroyuki MIYAJIMA, Tetsuya<br>TAURA, Haruo KOBAYASHI (Gunma Univ Japan)                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A Reduced Code Linearity Test Method for Pipelined A/D Converters<br>Jin-Fu LIN, Te-Chieh KUNG, Soon-Jyh CHANG (National Cheng Kung Univ Taiwan)                                                                                                    |

| Testing LCD Source Driver IC with Built-on-Scribe-Line Test Circuitry<br>Jui-Jer HUANG (National Taiwan Univ Taiwan), Chuan-Che LEE (Himax<br>Technologies - Taiwan), Jiun Lang HUANG (National Taiwan Univ Taiwan)                                 |

| Nov 26th, 2008                                                                                                                                                                                                                                      |

| 9:00-10:15 Session 5A: Delay Testing                                                                                                                                                                                                                |

| ldentifying Non-Robust Untestable RTL Paths in Circuits with Multi-Cycle Paths<br>Thomas Edison YU, Tomokazu YONEDA, Satoshi OHTAKE, Hideo FUJIWARA (NAIST -<br>Japan)                                                                              |

| High Quality Pattern Generation for Delay Defects with Functional Sensitized Paths<br>Ming-Ting HSIEH, Shun-Yen LU, Jing-Jia LIOU (National Tsing Hua Univ Taiwan),<br>Augusli KIFLI (Faraday - Taiwan)                                             |

| Refining Delay Test Methodology Using Knowledge of Asymmetric Transition Delay<br>Sean WU (UCSB - USA), Sreejit CHAKRAVARTY, Alexander TETELBAUM (LSI - USA), Li-<br>Chung WANG (UCSB - USA)                                                        |

| 9:00-10:15 Session 5B: Special Session: Analog Production Test 1                                                                                                                                                                                    |

| Effects of Advances in Analog, Mixed Signal and IO circuits on Test Strategies Salem ABDENNADHER (Intel - USA)                                                                                                                                      |

| Electrical Overstress Prevention & Test Best Practices<br>Leslie KHOO (National Semiconductor - Malaysia)                                                                                                                                           |

| Low Distortion Sine Waveform Generation by an AWG<br>Akinori MAEDA (Verigy - Japan)                                                                                                                                                                 |

| 9:00-10:15 Session 5C: Hybrid Method for Test Data Compression                                                                                                                                                                                      |

| An Effective Hybrid Test Data Compression Method Using Scan Chain Compaction and<br>Dictionary-based Scheme<br>Taejin KIM, Sunghoon CHUN, Yongjoon KIM, Myung-Hoon YANG, Sungho KANG (Yonsei<br>Univ Korea)                                         |

| Optimizing Test Data Volume Using Hybrid Compression<br>Brion KELLER, Sandeep BHATIA, Thomas BARTENSTEIN, Brian Foutz, Anis UZZAMAN<br>(Cadence - USA)                                                                                              |

| Cost Efficient Methods to Improve Performance of Broadcast Scan<br>Seongmoon WANG, Wenlong WEI (NEC Labs America - USA)                                                                                                                             |

| 10:45-12:00 Session 6A: Fault Diagnosis                                                                                                                                                                                                             |

| Hyperactive Faults Dictionary to Increase Diagnosis Throughput<br>Chen LIU (Univ.of Iowa - USA), Wu-Tung CHENG, Huaxing TANG (Mentor Graphics -<br>USA), Sudhakar M. REDDY (Univ. of Iowa - USA), Wei ZOU, Manish SHARMA (Mentor<br>Graphics - USA) |

|                                                                                                                                                                                                                                                     |

| Enhancing Transition Fault Model for Delay Defect Diagnosis<br>Wu-Tung CHENG, Brady BENWARE, Ruifeng GUO, Kun-Han TSAI, Takeo KOBAYASHI,<br>Kazuyuki Maruo (Mentor Graphics - USA), Michinobu NAKAO, Yoshiaki FUKUI (Renesas<br>- Japan), Hideyuki OTAKE (Renesas Design - Japan) |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Observation Point Oriented Deterministic Diagnosis Pattern Generation (DDPG) for<br>Chain Diagnosis<br>Fei WANG, Yu HU (ICT/CAS - China), Yu HUANG (Mentor Graphics - USA), Jing YE<br>(Peking Univ China), Xiaowei LI (ICT/CAS - China)                                          |

| 10:45-12:00 Session 6B: Special Session: Analog Production Test 2                                                                                                                                                                                                                 |

| The HiZ problem of Power Management IC testing<br>Hagen GOLLER (Verigy - Germany)                                                                                                                                                                                                 |

| Total Jitter Measurement for Testing HSIO Integrated SOCs<br>Takahiro YAMAGUCHI, Masahiro ISHIDA (Advantest Labs - Japan)                                                                                                                                                         |

| Load-Board/PCB Noise Suppression via Electromagnetic Band Gap Power Plane<br>Patterning<br>Fidel MURADALI (National Semiconductor - USA), Suzanne HUH, Madhavan<br>SWAMINATHAN (Georgia Inst. of Tech USA)                                                                        |

| 10:45-12:00 Session 6C: Defect Based Testing                                                                                                                                                                                                                                      |

| Defect Detection Rate through IDDQ for Production Testing<br>Junichi HIRASE (JST - Japan)                                                                                                                                                                                         |

| Variation Aware Analysis of Bridging Fault Testing<br>Urban INGELSSON, Bashir M. AL-HASHIMI (Univ. of Southampton - UK), Peter HARROD<br>(ARM - UK)                                                                                                                               |

| Prioritizing the Application of DFM Guidelines Based on the Detectability of<br>Systematic Defects<br>Dongok KIM, Irith POMERANZ (Purdue Univ USA), M. Enamul AMYEEN., Srikanth<br>VENKATARAMAN (Intel - USA)                                                                     |

| 13:30-14:45 Session 7A: Panel: How to Increase the Effectiveness of Yield Diagnostics - Is DFM the Answer to This?                                                                                                                                                                |

| Organizer/Moderator:<br>Anis Uzzaman (Cadence Design Systems, Inc USA)                                                                                                                                                                                                            |

| Panelists:<br>Adit Singh (Auburn University - USA)<br>Srinivas Patil (Intel Corporation - USA)<br>Sreejit Chakravarty (LSI Corporation - USA)<br>Brady Benware (Mentor Graphics Corporation - USA)<br>Sumio Kuwabara (NEC Electronics Corporation - Japan)                        |

| 13:30-14:45 Session 7B: Power Aware Test Generation                                                                                                                                                                                                                               |

| Targeting Leakage Constraints during ATPG<br>Goerschwin FEY (Univ. of Bremen - Germany), Satoshi KOMATSU (Univ. of Tokyo -<br>Japan), Yasuo FURUKAWA (Advantest - Japan), Masahiro FUJITA (Univ. of Tokyo -<br>Japan)                                                             |

| Power Management for Wafer-Level Test During Burn-In<br>Sudarshan BAHUKUDUMBI, Krishnendu CHAKRABARTY (Duke Univ USA)                                                                                                                                                             |

Test Generation for State Retention Logic Krishna CHAKRAVADHANULA, Vivek CHICKERMANE, Brion KELLER, Patrick GALLAGHER, Steven GREGOR (Cadence - USA)

13:30-14:45 Session 7C: Design for Efficient Test

Area and Test Cost Reduction for On-Chip Wireless Test Channels with System-Level Design Techniques Chun-Kai HSU, Li-Ming DENQ, Mao-Yin WANG, Jing-Jia LIOU, Chih-Tsun HUANG, Cheng-Wen WU (National Tsing Hua Univ. - Taiwan)

On-Chip Test Generation Mechanism for Scan-Based Two Pattern Tests Nan-Cheng LAI, Sying-Jyan WANG (National Chung-Hsing Univ. - Taiwan)

Level-Testability of Multi-Operand Adders Nobutaka KITO, Naofumi TAKAGI (Nagoya Univ. - Japan)

#### 15:15-17:00 Session 8A: Industry Session

System Level LBIST Implementation Fei ZHUANG, Xiangfeng LI, Junbo JIA (Cisco Systems - China)

CooLBIST : An Effective Approach of Test Power Reduction for LBIST Jun MATSUSHIMA, Yoichi MAEDA, Masahiro TAKAKURA (Renesas Technology Corp. - Japan)

Practical Challenges in Logic BIST Implementation - Case Studies Shianling WU (SynTest Technologies, Inc. - USA), Hiroshi FURUKAWA (Kyushu Institute of Technology - Japan), Boryau SHEU, Laung-Terng WANG, Hao-Jan CHAO, Lizhen YU (SynTest Technologies, Inc. - USA), Xiaoqing WEN (Kyushu Institute of Technology - Japan), Michio MURAKAMI (SynTest Technologies, Inc. - USA)

USB2.0 Logic Built In Self Test Methodology Kean Hong BOEY, Wai Mun NG, Kok Sing YAP (Intel Microelectronics (M) Sdn. Bhd. -Malaysia)

Shared At-Speed BIST for Parallel Test of SRAMs with Different Address Sizes Tomonori SASAKI, Yoshiyuki NAKAMURA, Toshiharu ASAKA (NEC Electronics Corporation - Japan)

Experimental Results of Built-In JItter Measurement for Gigahertz Clock Nai-Chen Daniel CHENG, Yu LEE, Ji-Jan CHEN (Industrial Technology Research Institute - Taiwan)

Leading Edge Technology and Test Noise Takayuki KATAYAMA, Kou EBIHARA, Goro IMAIZUMI (Fujitsu Microelectronics Limited - Japan)

DFT Technique to Conclusively Translate Floating Nodes to High IDDQ Current in Analog Circuits Ricky SMITH, Tony SHI (Texas Instruments - USA)

Diagnosis of Voltage Dependent Scan Chain Failure Using VBUMP Scan Debug Method Khairul KHUSYARI, Wei Tee NG, Neal JAARSMA, Robert ABRAHAM, Peng Weng NG, Boon Hui ANG, Chin Hu ONG (Marvell Semiconductor - Malaysia)

Detectability of the Two-dimensional Detector for Time Resolved Emission Measurement Nobuyuki HIRAI (Hamamatsu Photonics K.K. - Japan)

Protocol Aware Test Methodologies Using Today's ATE

Shawn MOLAVI, Andy EVANS, Ray CLANCY (Broadcom Corp. - USA)

15:15-16:55 Session 8B: SoC Test

Core-Level Compression Technique Selection and SOC Test Architecture Design Anders LARSSON, Xin ZHANG, Erik LARSSON (Linköping Univ. - Sweden), Krishnendu CHAKRABARTY (Duke Univ. - USA)

Simulation-Driven Thermal-Safe Test Time Minimization for System-on-Chip Zhiyuan HE, Zebo PENG, Petru ELES (Linköping Univ. - Sweden)

A Design-for-Debug (DfD) for NoC-based SoC Debugging via NoC Hyunbean YI (Univ. of Massachusetts - USA), Sungju PARK (Hanyang Univ. - Korea), Sandip KUNDU (Univ. of Massachusetts - USA)

Accelerated Functional Testing of Digital Microfluidic Biochips Debasis MITRA (Indian Statistical Inst. - India), Sarmishtha GHOSHAL, Hafizur RAHAMAN (Bengal Engg. and Science Univ. - India), Bhargab B. BHATTACHARYA, D. Dutta MAJUMDER (Indian Statistical Inst. - Japan), Krishnendu CHAKRABARTY (Duke Univ. - USA)

#### 15:15-16:55 Session 8C: Design Verification and Validation

On Reusing Test Access Mechanisms for Debug Data Transfer in SoC Post-Silicon Validation Xiao LIU, Qiang XU (Chinese Univ. of Hong Kong - Hong Kong)

A Robust Automated Scan Pattern Mismatch Debugger Kun-Han TSAI, Ruifeng GUO, Wu-Tung CHENG (Mentor Graphics - USA)

An Interactive Verification and Debugging Environment by Concrete/Symbolic Simulations for System-level Designs Yoshihisa KOJIMA, Tasuku NISHIHARA, Takeshi MATSUMOTO, Masahiro FUJITA (Univ. of Tokyo - Japan)

Coverage Directed Test Generation: Godson Experience HaiHua SHEN, Wenli WEI, Yunji CHEN, Bowen CHEN and Qi GUO (ICT/CAS - China)

Nov 27th, 2008

9:00-10:15 Session 9A: Power Aware Scan Test

Test Power Reduction by Blocking Scan Cell Outputs Xijiang LIN, Janusz RAJSKI (Mentor Graphics - USA)

Two-Gear Low-Power Scan Test Chao-Wen TZENG, Shi-Yu HUANG (National Tsing-Hua Univ. - Taiwan)

DCScan: A Power-Aware Scan Testing Architecture Gui DAI, Zhiqiang YOU, Jishun KUANG, Jiedi HUANG (Hunan Univ. - China)

9:00-10:15 Session 9B: Memory Self Test

Layout-Aware and Programmable Memory BIST Synthesis for Nanoscale System-on-Chip Designs Aman KOKRADY, C.P. RAVIKUMAR (TI - India), Nitin CHANDRACHOODAN (IIT Madras -India)

A Low-Cost Pipelined BIST Scheme for Homogeneous RAMs in Multicore Chips

| n Asian Test Symposium (ATS 2008) |                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   | Yu-Jen HUANG, Jin-Fu LI (National Central Univ Taiwan)                                                                                                                                                                                                                                                                                                        |

|                                   | A Software-Based Test Methodology for Direct-Mapped Data Cache<br>Yi-Cheng LIN, Yi-Ying TSAI, Kuen-Jong LEE, Cheng-Wei YEN, Chung-Ho CHEN<br>(National Cheng Kung Univ Taiwan)                                                                                                                                                                                |

|                                   | 9:00-10:15 Session 9C: On-Line Test                                                                                                                                                                                                                                                                                                                           |

|                                   | Time-Multiplexed Online Checking: A Feasibility Study<br>Ming GAO, Hsiu-Ming CHANG, Peter LISHERNESS, Kwang-Ting CHENG (UCSB - USA)                                                                                                                                                                                                                           |

|                                   | On-Line Instruction-checking in Pipelined Microprocessors<br>Stefano DI CARLO (Politecnico di Torino - Italy), Giorgio DI NATALE (LIRMM - France),<br>Riccardo MARIANI (YOGITECH - Italy)                                                                                                                                                                     |

|                                   | Design of FSM with Concurrent Error Detection Based on Viterbi Decoding<br>Ming LI, Shiyi XU, Enjun XIA, Fayu WAN (Shanghai Univ China)                                                                                                                                                                                                                       |

|                                   | 10:45-12:00 Session 10A: Power Aware Delay Testing                                                                                                                                                                                                                                                                                                            |

|                                   | PHS-Fill: A Low Power Supply Noise Test Pattern Generation Technique for At-Speed<br>Scan Testing in Huffman Coding Test Compression Environment<br>Yi-Tsung LIN, Meng-Fan WU, Jiun-Lang HUANG (National Taiwan Univ Taiwan)                                                                                                                                  |

|                                   | CTX: A Clock-Gating-Based Test Relaxation and X-Filling Scheme for Reducing Yield<br>Loss Risk in At-Speed Scan Testing<br>Hiroshi FURUKAWA, Xiaoqing WEN, Kohei MIYASE, Yuta YAMATO, Seiji KAJIHARA<br>(Kyushu Inst. of Tech Japan), Patrick GIRARD (LIRMM - France), Laung-Terng<br>WANG (SynTest - USA), Mohammad TEHRANIPOOR (Univ. of Connecticut - USA) |

|                                   | Power Analysis and Reduction Techniques for Transition Fault Testing<br>Khushboo AGARWAL, Srinivas VOOKA, Srivaths RAVI, Rubin PAREKHJI, Arjun Singh<br>GILL (TI - India)                                                                                                                                                                                     |

|                                   | 10:45-12:00 Session 10B: Advanced Memory Test                                                                                                                                                                                                                                                                                                                 |

|                                   | Influence of Parasitic Capacitance Variations on 65nm and 32nm Predictive Model<br>Technology SRAM Core-Cells<br>Stefano DI CARLO, Alessandro SAVINO, Alberto SCIONTI, Paolo PRINETTO (Politecnico<br>di Torino - Italy)                                                                                                                                      |

|                                   | Test and Diagnosis Algorithm Generation and Evaluation for MRAM Write Disturbance<br>Fault<br>Wan-Yu LO, Ching-Yi CHEN, Chin-Lung SU, Cheng-Wen WU (National Tsing Hua Univ.<br>- Taiwan)                                                                                                                                                                     |

|                                   | GDDR5 Training - Challenges and Solutions for ATE-based Test<br>Hubert WERKMANN, Dong-Myong KIM (Verigy - Germany), Shinji FUJITA (Verigy -<br>Japan)                                                                                                                                                                                                         |

|                                   | 10:45-12:00 Session 10C: Fault Tolerance and Dependable System                                                                                                                                                                                                                                                                                                |

|                                   | A Re-design Technique of Datapath Modules in Error Tolerant Applications<br>Doochul SHIN, Sandeep K. GUPTA (USC - USA)                                                                                                                                                                                                                                        |

|                                   | Reliable Network-on-Chip Router for Crosstalk and Soft Error Tolerance<br>Ying ZHANG, Huawei LI, Xiaowei LI (ICT/CAS - China)                                                                                                                                                                                                                                 |

|                                   | Analyses on Trend of Accidents in Financial Information Systems Reported by<br>Newspapers from the Viewpoint of Dependability                                                                                                                                                                                                                                 |

|                                   |                                                                                                                                                                                                                                                                                                                                                               |

Koichi BANDO, Kenji TANAKA (Univ. of Electro-Communications - Japan)

The Seventeenth Asian Test Symposium November 24-27, 2008, <u>Keio Plaza Hotel Sapporo</u>, Sapporo, JAPAN

News: Ealry Registration closes on Oct. 24th, 2008.

#### **General Information**

- <u>Sponsors/Supporters</u>

- <u>Scope</u>

- <u>Key Dates</u>

- More Information

#### **Registration**

- Early Registration

Registration Form

[pdf/doc]

- <u>VISA Guide</u>

#### ATS'08 Program

- ATS'08 at a glance

- Advance Program

- <u>Tutorials</u>

- Keynote Speech/

- Invited Talk

- <u>Social Program</u>

#### **Accommodations**

- Hotel Reservation Guide

(at Keio Plaza Hotel

Sapporo)

- <u>Alternative Hotels</u>

#### **Conference Location**

- <u>The Venue</u>

- <u>Access</u>

- <u>Sapporo Convention</u> <u>Bureau</u>

- <u>Sapporo White Illumination</u>

<u>(in Japanese)</u>

#### **Call for Papers**

PDF version

#### Paper Submission

- <u>Regular Session</u>

<u>To WelCoMe system</u> (paper submission)

- Industrial Session

#### Committees

- Organizing Committee

- <u>Program Committee</u>

#### **Related Links**

<u>WRTLT'08</u> <u>(In conjunction with</u> <u>ATS'08)</u>

#### Tutorials

#### Tutorial 1

Statistical Screening Methods Targeting "Zero Defect" IC Quality and Reliability

Presenter: Adit Singh, Auburn University

#### Summary:

Integrated circuits have traditionally all been tested identically in the manufacturing flow. However, as the detection of subtle manufacturing flaws becomes ever more challenging and expensive in aggressively scaled nanometer technologies, innovative new statistical screening methods are being developed that attempt to improve test effectiveness and optimize test costs by adaptively subjecting "suspect" parts to more extensive testing. The idea is similar to security screening at airports. Such methods fall into two broad categories: those that exploit the statistics of defect distribution on wafers, and those that exploit the correlation in the variation of process and performance parameters on wafers. This tutorial presents test methodologies that span both these categories, and illustrates their effectiveness with results from a number of recently published experimental studies on production circuits from IBM, Intel and LSI Logic, and NXP Semiconductor.

#### Tutorial 2

**Delay Testing: Theory and Practice**

Presenters: Srinivas Patil, Intel Corporation Sreejit Chakravarty, LSI Corporation

#### Summary:

The goal of this tutorial is to provide the background and knowledge of DFT methods, tools/methodologies and best-known industry practices necessary for implementation of delay test methodology on both custom and ASIC designs. To that end, this tutorial will cover the following key aspects of delay tests: (1) Delay test models and test application techniques, (2) Incorporating environmental conditions such as cross-talk and power droop in delay tests, (3) DFT design techniques to support scan-based delay test, (4) Relevant tools and methodologies and (5) Representative test case studies from the industry. The focus of the tutorial will be primarily scan-based delay tests with emphasis on real-world implementation using industrial case studies. On the theory front, the emphasis will be on the easy to understand theoretical concepts related to delay test, and not on the complicated algebra and theory which accompanies many theoretical works on delay test.

The Seventeenth Asian Test Symposium November 24-27, 2008, <u>Keio Plaza Hotel Sapporo</u>, Sapporo, JAPAN

News: Ealry Registration closes on Oct. 24th, 2008.

#### **General Information**

- Sponsors/Supporters

- <u>Scope</u>

- <u>Key Dates</u>

- More Information

#### **Registration**

- Early Registration

Registration Form

[pdf/doc]

- <u>VISA Guide</u>

#### ATS'08 Program

- ATS'08 at a glance

- Advance Program

- <u>Tutorials</u>

- Keynote Speech/

- Invited Talk

Social Program

#### Accommodations

- Hotel Reservation Guide

(at Keio Plaza Hotel

Sapporo)

- <u>Alternative Hotels</u>

#### **Conference Location**

- The Venue

- <u>Access</u>

- <u>Sapporo Convention</u>

<u>Bureau</u>

- <u>Sapporo White Illumination</u>

<u>(in Japanese)</u>

#### Call for Papers

• PDF version

#### Paper Submission

- <u>Regular Session</u>

<u>To WelCoMe system</u> (paper submission)

- Industrial Session

#### Committees

- Organizing Committee

- <u>Program Committee</u>

#### **Related Links**

<u>WRTLT'08</u> (<u>In conjunction with</u> <u>ATS'08)</u>

#### Keynote Speech & Invited Talk

Keynote Speech 1 (Nov. 25th, 9:20-9:45)

The Value of Extending Test Solutions

Presenter: Brian STEVENS (National Semiconductor - USA)

#### Summary:

In contemporary semiconductor product creation, de-compartmentalizing and applying previously operation-specific knowledge into different functional areas is valuable. This talk presents several examples of how test engineering expertise in an analog company was levered across functional area boundaries to help solve unique technical challenges and reduce overall new product cycle time. In this direction, the audience is urged to re-examine all processes related to semiconductor product development and further the trend of extending test innovation beyond traditional definitions and applications.

#### Keynote Speech 2 (Nov. 25th, 9:45 - 10:10)

Architectural Evolution and Test Requirements in Digital-Convergence Era

Presenter: Kunio UCHIYAMA (Hitachi - Japan)

#### Summary:

For digital systems in the digital-convergence era, various functions such as communication, security, audio, video, and recognition are required in a single device. However, improving the operating frequency of an embedded LSI in the system is saturated due to the significantly increasing power consumption problem. To solve this difficulty, the architecture of an LSI has been changing greatly these few years. This talk will review the recent architecture that targets a superior performance-per-power ratio and functional flexibility and the requirements to test the newly architected SoC. As the future mainstream direction, a parallelizing architecture that places multiple CPUs and special-purpose processors on a chip and that uses a parallelizing compiler will be discussed. Reviewing the low-power circuit and device technologies that support this multi-core architecture, test requirements will also be discussed.

#### Invited Talk 1 (Nov. 25th, 10:40-11:20)

The role of DFT in Yield

Presenter: Brady BENWARE (Mentor Graphics - USA)

Summary:

As technology nodes continue to scale, reaching mature yields in the same time as the previous node becomes increasingly difficult. In addition, mature yields are being eroded by design sensitivities to normal process variation. To combat these challenges, chip design is being called upon more than ever to help ensure designs are manufacturable and contain sufficient capabilities to determine the root cause of failures that arise in manufacturing. This presentation will first discuss the specific challenges in Yield Analysis and Failure Analysis that are resulting in slower yield ramps and lower mature yields. Secondly, a new approach to yield enhancement which effectively incorporates DFT technologies will be presented with silicon case studies that demonstrate specifically how DFT can contribute to solving yield problems in the nm era.

Invited Talk 2 (Nov. 25th, 11:20-12:00)

Issues and new Scenario for Deep sub-micron LSI design and Testing

Presenter: Kunihiro ASADA (University of Tokyo - Japan)

#### Summary:

The feature size of the LSI fabrication technologies is approaching to the extreme limit of the atomic size. Devices scaled down in LSI become more attractive in speed and power consumption, but less reliable and more variable in performance parameters. The reliability problem is caused by the miniaturized size and film thickness and some of variations in device parameters are physically intrinsic, caused by such as thermo-dynamic effects. One of the most important subjects in LSI design is to find a way to maximize the potential in performance with minimizing the essential weakness in device characteristics. In testing LSI, along with the conventional problems such as increasing complexity and decreasing observability/controllability, we will be faced with new issues of long term reliability and discrepancies between testing and real applications in terms of chip environments. We may have to give up the conventional scenario of the reliable prescreening of defect-prone LSI by testing-before-shipping. In the presentation, after reviewing issues to be faced soon in LSI design and testing, a new scenario to overcome the issues will be proposed as a possible design and testing collaboration in the extremely deep sub-micron LSI era.

The Seventeenth Asian Test Symposium November 24-27, 2008, Keio Plaza Hotel Sapporo, Sapporo, JAPAN

News: Ealry Registration closes on Oct. 24th, 2008.

#### **General Information**

- Sponsors/Supporters

- <u>Scope</u>

- Key Dates

- More Information

#### **Registration**

- Early Registration

Registration Form

[pdf/doc]

- <u>VISA Guide</u>

#### ATS'08 Program

- ATS'08 at a glance

- <u>Advance Program</u>

- <u>Tutorials</u>

- Keynote Speech/

- Invited Talk

Social Program

#### **Accommodations**

- Hotel Reservation Guide

(at Keio Plaza Hotel

Sapporo)

- <u>Alternative Hotels</u>

#### **Conference Location**

- The Venue

- <u>Access</u>

- <u>Sapporo Convention</u> <u>Bureau</u>

- <u>Sapporo White Illumination</u> (in Japanese)

#### Call for Papers

PDF version

#### Paper Submission

- <u>Regular Session</u>

<u>To WelCoMe system</u> (paper submission)

- Industrial Session

#### Committees

- Organizing Committee

- Program Committee

#### **Related Links**

<u>WRTLT'08</u> <u>(In conjunction with</u> <u>ATS'08)</u>

#### Welcom Reception

The welcome reception will be held in Keio Plaza Hotel Sapporo (Room: Rose) from 18:00 to 20:00, Nov. 24th.

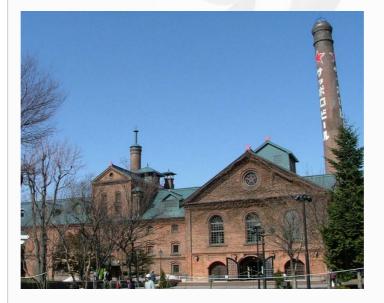

#### Tour to Beer Graden & Beer Party

The tour to <u>SAPPORO BIER GAETEN</u> (a famous beer garden of Sapporo) and the beer party at the garden will be held from 17:00 - 20:30, Nov. 25th.

- 17:00 18:00 Tour to Beer Garden

- 18:00 20:00 Beer Party

#### Banquet

The banquet will be held at Keio Plaza Hotel Sapporo (Room: Eminence A) from 18:00 to 20:00, Nov. 26th.

The Seventeenth Asian Test Symposium November 24-27, 2008, Keio Plaza Hotel Sapporo, Sapporo, JAPAN

News: Ealry Registration closes on Oct. 24th, 2008.

#### **General Information**

- <u>Sponsors/Supporters</u>

- <u>Scope</u>

- <u>Key Dates</u>

- More Information

#### **Registration**

- Early Registration

Registration Form

[pdf/doc]

- <u>VISA Guide</u>

#### ATS'08 Program

- ATS'08 at a glance

- Advance Program

- <u>Tutorials</u>

- <u>Keynote Speech/</u>

- Invited Talk

Social Program

### Accommodations

- Hotel Reservation Guide

(at Keio Plaza Hotel

Sapporo)

- <u>Alternative Hotels</u>

#### **Conference Location**

- The Venue

- <u>Access</u>

- <u>Sapporo Convention</u>

<u>Bureau</u>

- <u>Sapporo White Illumination</u>

<u>(in Japanese)</u>

#### Call for Papers

PDF version

#### Paper Submission

- <u>Regular Session</u>

<u>To WelCoMe system</u> (paper submission)

- Industrial Session

#### Committees

- Organizing Committee

- Program Committee

#### **Related Links**

<u>WRTLT'08</u> (<u>In conjunction with</u> <u>ATS'08</u>)

#### Accommodations

Hotel Reservation Guide at Keio Plaza Hotel Sapporo

ATS hotel reservation has been closed. Please make your reservation through Keio Plaza Hotel Web site or other travel agencies.

#### **ACCOMMODATIONS**

Reservation will be made on a first-come, first-served basis. The room rates are valid only during the period of the symposium, i.e. from Nov. 23 to Nov. 26.

#### **APPLICATIONS**

Persons who wish to reserve hotel accommodations should complete the application no later than October 24, 2008. After October 24, hotel rooms may not be guaranteed. Applications will be accepted via e-mail or fax. Please indicate your order of preference in the application form. We will send a confirmation to your e-mail. If you have not received a confirmation in one week, please notify us by email: yanagi4@ee.tokushima-u.ac.jp

#### <u>PAYMENT</u>

Payments must be made on site by cash or by credit cards. Bank transfer and personal check are NOT available.

#### CANCELLATION POLICY

The cancellation can be made by email: yanagi4@ee.tokushima-u.ac.jp until Nov. 16.

After Nov. 17, all changes and cancellations should be directed to the hotel. Cancellation must be made **72 hours** prior to arrival.

#### ACCOMMODATION FEE

| Room | Room Type                | Accommodation fees *         |                                          |  |

|------|--------------------------|------------------------------|------------------------------------------|--|

| Code | Коопттуре                | Nov. 23                      | Nov. 24 - 26                             |  |

|      |                          |                              | 8,500 JPY                                |  |

|      | Single Room<br>(Smoking) | (price per person per night) | (price per person per night)             |  |

|      |                          |                              | 16,000 JPY<br>(price per two persons per |  |

|      | Twin Room                | (price per two persons per   | (price per two persons per               |  |

| est Symposium (ATS 2008) |                                                                                                                                                                                                                                                      |                   |                     |                          |              |  |  |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------|--------------------------|--------------|--|--|--|