# November 16-19, 2014. Hangzhou, China The 23rd Asian Test Symposium

# **General Information**

Symposium Overview

News

Committee

Contact Us

## The Symposium

Date&Location

**VISA**

Venue

Accommodation

Registration

# Technical Program

Keynote & Invited Talks

**Tutorial**

Advance Program

For Speakers

For Session Chairs

Social Event

#### Submissions

Call for Papers

Electronic Paper Submission

**Doctoral Thesis Award**

#### Related Links

**IEEE TTTC**

WRTLT'14

**ATS History**

#### NEWS

2014/11/06 On-site Registration

2014/08/26 Registration System online.

2014/08/09 <u>Accepted Papers</u>.

2014/05/07 ATS Doctoral Thesis Award.

2014/05/04 <u>Submission system is opened.</u>

2014/04/24 ATS Best Paper Award.

Important Deadlines

**Sponsors**

Submission deadline: May. 23,2014 IEEE Computer Society

Notification of acceptance: Aug. 10, 2014 Test Technology Technical Council

Camera ready manuscript: Sept. 05, 2014 Institute of Computing Technology

Best Paper Award: ATS'14 will present a Best Paper Award to a selected paper of exceptional quality. The evaluation will be conducted by an award committee constituted by experts covering all aspects of test technology, based on the criteria of innovation, potential impact, and presentation quality.

**Diamond Supporter:**

Silver Supporter:

Sponsored by:

China Computer Federation

In cooperation with Zhejiang A & F University, China

It's recommended that you access this website using IE7 or Firefox

Conference Admin

# November 16-19, 2014. Hangzhou, China The 23rd Asian Test Symposium

## General Information

Symposium Overview

News

Committee

Contact Us

# The Symposium

Date&Location

**VISA**

Venue

Accommodation

Registration

# **Technical Program**

Keynote & Invited Talks

**Tutorial**

Advance Program

For Speakers

For Session Chairs

Social Event

#### Submissions

Call for Papers

Electronic Paper Submission

**Doctoral Thesis Award**

#### Related Links

IEEE TTTC

WRTLT'14

**ATS History**

# Symposium Overview

The Asian Test Symposium (ATS) provides an open forum for researchers and industrial practitioners from all countries of the world, especially from Asia, to exchange innovative ideas on system, board, and device testing with design, manufacturing and field consideration in mind.

#### Original papers on, but not limited to, the following areas are invited.

- Automatic Test Pattern Generation

- Fault Modeling and Simulation

- Design Verification and Validation

- Diagnosis and Debug

- Board and System Test

- Analog/Mixed-Signal Test

- High-Speed I/O Test

- RF Test

- Delay and Performance Test

- Memory Test/FPGA Test

- System-in-Package/3D Test

- Software Testing

- Boundary Scan Test

- Built-In Self-Test

- · Design-for-Testability

- Test Compression

- On-Line Test

- Temperature/Power-Aware Testing

- · Defect-Based Testing

- · Fault Tolerance

- Dependable System

- Yield Analysis and Enhancement

- Test Quality

- · Economics of Test

- Hardware Security

#### **Submissions**

**Regular Sessions**: The ATS'14 Program Committee invites original, unpublished paper submissions on the above topics. Paper submissions should be complete manuscripts, not exceeding six pages (including figures, tables, and bibliography) in a standard IEEE two-column format. The submission will be considered evidence that upon acceptance the author(s) will submit a final camera-ready version of the paper for inclusion in the proceedings, and will present the paper at the symposium. The registration of at least one author is required for publication.

ATS'14 will present a Best Paper Award to a selected paper of exceptional quality. The evaluation will be conducted by an award committee constituted by experts covering all aspects of test technology, based on the criteria of innovation, potential impact, and presentation quality.

# **Key Dates**

| Submission deadline:        | May 16, 2014 May 23,2014(extended) |

|-----------------------------|------------------------------------|

| Notification of acceptance: | Aug. 10, 2014                      |

| Camera ready manuscript:    | Sept. 5, 2014                      |

#### **Further Information**

Email: ats14@ict.ac.cn

URL: http://ats2014.ict.ac.cn

**Diamond Supporter:**

Silver Supporter:

Sponsored by:

It's recommended that you access this website using IE7 or Firefox

Conference Admin

# November 16-19, 2014. Hangzhou, China The 23rd Asian Test Symposium

# General Information

Symposium Overview

News

Committee

Contact Us

# The Symposium

Date&Location

**VISA**

Venue

Accommodation

Registration

# Technical Program

Keynote & Invited Talks

**Tutorial**

Advance Program

For Speakers

For Session Chairs

Social Event

#### Submissions

Call for Papers

Electronic Paper Submission

**Doctoral Thesis Award**

## **Related Links**

IEEE TTTC

WRTLT'14

**ATS History**

## **News**

Date Contents

2014/08/09 Accepted Papers

2014/05/12 Submission deadline is extended to May 23.

2014/05/07 <u>ATS Doctoral Thesis Award.</u>2014/05/04 Submission System is Opened!

It's recommended that you access this website using IE7 or Firefox

Conference Admin

# November 16-19, 2014. Hangzhou, China The 23rd Asian Test Symposium

# General Information

Symposium Overview

News

Committee

Contact Us

# The Symposium

Date&Location

**VISA**

Venue

Accommodation

Registration

# **Technical Program**

Keynote & Invited Talks

**Tutorial**

Advance Program

For Speakers

For Session Chairs

Social Event

## Submissions

Call for Papers

Electronic Paper Submission

**Doctoral Thesis Award**

#### Related Links

**IEEE TTTC**

WRTLT'14

**ATS History**

## **Organizing Committee**

General Co-Chair(s)

Huawei Li, Institute of Computing Technology, Chinese Academy of Sciences

Krishnendu Chakrabarty, Duke University

Program Co-Chair(s)

Yinhe Han, Institute of Computing Technology, Chinese Academy of Sciences

Qiang Xu, The Chinese University of Hong Kong

Tutorial Chair

Ying Zhang, Tongji University

· Publicity Chair

Jiun-Lang Huang, National Taiwan University

Publication Chair

Guihai Yan, Institute of Computing Technology, Chinese Academy of Sciences

· A/V Chair

Li Jiang, Shanghai Jiaotong University

Web Chair

Long Tian, Institute of Computing Technology, Chinese Academy of Sciences

Finance Chair

Lei Zhang, Institute of Computing Technology, Chinese Academy of Sciences

· Local Arrangement Chair

Guanghui Li, Zhejiang A&F University

Registration Chair

Tiancheng Wang, Institute of Computing Technology, Chinese Academy of Sciences

· North American Liaison

Kwang-Ting (Tim) Cheng, University of California at Santa Barbara

European Liaison

Zebo Peng, Linkoping University, Sweden

#### **Program Committee**

Erik Jan Marinissen Dong Xiang

Yu Hu Shiyi Xu

Patrick Girard Hans-Joachim Wunderlich

Virendra Singh Cecilia Metra

Yoshinobu Higami Kazumi Hatayama

Seiji Kajihara Michiko Inoue

Kazuteru Namba Yasuo Sato

Masaki Hashizume Xiaoqing Wen

Sungho Kang Said Hamdioui

Stefan Eichenberger Anzhela Matrosova

Erik Larsson Chien-Mo Li

Chih-Tsun Huang Hao-Chiao Hong

Jin-Fu Li Jing-Jia Liou

Kuen-Jong Lee Chia-Tso Chao

Hung-Pin Wen Shyue-Kung Lu

Shu-Min Li Shi-Yu Huang

Alex Orailoglu Krishna Chakravadhanula

Hans Tsai Hsiu-Ming (Sherman) Chang

Li-C Wang Michael S.Hsiao

Irith Pomeranz Peilin Song

Michel Renovell Rohit Kapur

Sandeep Gupta Mohammad Tehranipoor

Nur A.Touba Vishwani Agrawal

Vivek Chickermane Wen-Ben Jone

Peter Wohl Xinli Gu

Yi-Shing Chang Yu Huang

Adam Osseiran Chia Yee Ooi

Karim Arabi Sule Ozev

Danella Zhao Feng Yuan

Jun Liu Song Jin

Gefu Xu Feng Shi

Chunsheng Liu Yier Jin

Zhaobo Zhang Xiaochun Yu

Rishad A Shafik Khursheed Saqib

Ke Huang Li Jiang

Lingyi Liu Xiaoxin Fan

Ming Gao Dimitris Gizopoulos

## **Steering Committee**

· Chair

Kuen-Jong Lee, National Cheng Kung University, Taiwan

· Vice-Chair

Masaki Hashizume, University of Tokushima, Japan

#### Members

Bhargab Bhattacharya, Indian Statistical Institute, India

Krishnendu Chakrabarty, Duke University, USA

Michiko Inoue, Nara Institute of Science and Technology, Japan

Patrick Girard, LIRMM / CNRS, France

Shi-yu Huang, National Tsing Hua University, Taiwan

Jinn-Lang Huang, National Taiwan University, Taiwan

Tomoo Inoue, Hiroshima City University, Japan

Seiji Kajihara, Kyushu Institute of Technology, Japan

Huawei Li, Chinese Academy of Sciences, China

Xiaowei Li, Chinese Academy of Sciences, China

Virendra Singh, Indian Institute of Science, India

Hiroshi Takahashi, Ehime University, Japan

Sying-Jyan Wang, National Chung Hsing University, Taiwan

Shiyi Xu, Shanghai University, China

#### · Past Chairs

~2000: Kozo Kinoshita, Osaka University, Japan

2001-2004: Hideo Fujiwara, Nara Institute of Science and Technology, Japan

2005-2006: Cheng-Wen Wu, National Tsing Hua University, Taiwan

2007-2010: Seiji Kajihara, Kyushu Institute of Technology, Japan

2011-2013: Xiaowei Li, Chinese Academy of Sciences, China

It's recommended that you access this website using IE7 or Firefox

Conference Admin

# November 16-19, 2014. Hangzhou, China The 23rd Asian Test Symposium

# **General Information**

Symposium Overview

News

Committee

Contact Us

# The Symposium

Date&Location

**VISA**

Venue

Accommodation

Registration

# Technical Program

Keynote & Invited Talks

**Tutorial**

Advance Program

For Speakers

For Session Chairs

Social Event

## **Submissions**

Call for Papers

Electronic Paper Submission

**Doctoral Thesis Award**

## **Related Links**

**IEEE TTTC**

WRTLT'14

**ATS History**

#### **Contact Us**

Please feel free to contact us if you have any question. Thank you.

Conference Program Chair: Yinhe Han

Email: yinhes@ict.ac.cn

Conference Web Chair: Long Tian

Email: tianlong@ict.ac.cn Tel:(010)62600718

It's recommended that you access this website using IE7 or Firefox

Conference Admin

# November 16-19, 2014. Hangzhou, China The 23rd Asian Test Symposium

# General Information

Symposium Overview

News

Committee

Contact Us

# The Symposium

Date&Location

**VISA**

Venue

Accommodation

Registration

# Technical Program

Keynote & Invited Talks

**Tutorial**

Advance Program

For Speakers

For Session Chairs

Social Event

## Submissions

Call for Papers

Electronic Paper Submission

**Doctoral Thesis Award**

## **Related Links**

IEEE TTTC

WRTLT'14

**ATS History**

# **Date & Location**

The 2014 ATS will be held at Nov.16-19, 2014, Hangzhou, China.

It's recommended that you access this website using IE7 or Firefox

Conference Admin

# November 16-19, 2014. Hangzhou, China The 23rd Asian Test Symposium

## General Information

Symposium Overview

News

Committee

Contact Us

# The Symposium

Date&Location

**VISA**

Venue

Accommodation

Registration

# **Technical Program**

Keynote & Invited Talks

**Tutorial**

Advance Program

For Speakers

For Session Chairs

Social Event

#### Submissions

Call for Papers

Electronic Paper Submission

**Doctoral Thesis Award**

#### Related Links

**IEEE TTTC**

WRTLT'14

**ATS History**

## **VISA**

- Visas are needed for most non-Chinese nationals to enter China (exceptions are passport holders from Singapore, Brunei, and Japan). Application should be made to the Chinese Embassy/Consulate in your country of residence. There are two types of visas, Tourist Visa (L Visa) and Business Visa (F Visa).

- For a Tourist Visa, you should check with the Chinese Embassy/Consulate in your country of residency to determine the local rules that apply for your tourist visa application. You may need to show evidence of bookings for your return flights and hotel. For most countries, a Tourist Visa does not require an official invitation letter.

- In China, invitation letters are issued by the Ministry of Foreign Affairs. We need about one month to apply it after we receive your request. Therefore, we strongly recommend you to apply for the Tourist Visa. If an invitation letter is still required, please let us know.

- To request an invitation letter, you need first <u>register</u> for the conference and then forward the registration confirmation email, along with your request to ats14@ict.ac.cn.

- Citizens from many countries can enter Hongkong without a visa. For those

who do plan to go through Hongkong, please note that you still need a

Chinese Visa to enter Shenzhen. If you will travel between Hongkong and

Shenzhen multiple times, you need to apply for a multi-entry visa.

- We expect that most attendees can use a Tourist Visa.

- An official invitation letter is required to apply for a Business Visa.

- You can find the website of Chinese Embassy/Consulate in your country from here.

Please feel free to contact us if you have any question about VISA. Thank you.

It's recommended that you access this website using IE7 or Firefox

Conference Admin

# November 16-19, 2014. Hangzhou, China The 23rd Asian Test Symposium

## General Information

Symposium Overview

News

Committee

Contact Us

# The Symposium

Date&Location

**VISA**

Venue

Accommodation

Registration

# **Technical Program**

Keynote & Invited Talks

**Tutorial**

Advance Program

For Speakers

For Session Chairs

Social Event

#### Submissions

Call for Papers

Electronic Paper Submission

**Doctoral Thesis Award**

#### Related Links

IEEE TTTC

WRTLT'14

**ATS History**

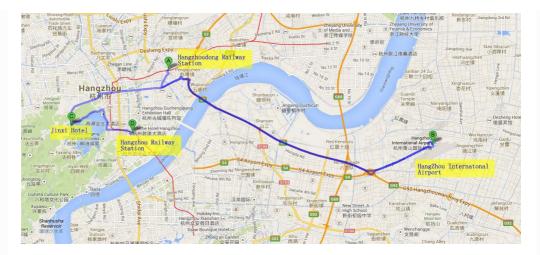

#### Venue

The 2014 ATS will be held in the Hangzhou Jinxi Hotel.

#### Address:

Hangzhou Jinxi Hotel

No.39 Causeway yang ,Hangzhou, China

TEL: (+86)0571-87992288-6901

• To receive the conference discount rate for Hangzhou Jinxi Hotel, please fill and return *this form* via e-mail to *ats14@ict.ac.cn* by **October 15, 2014.**

#### **Conference Transportation**

#### 1) Arriving at the Xiaoshan airport

The map from Airport of Xiaoshan to Jinxi Hotel.

Upon Arriving at the Xiaoshan airport, we recommend two ways to get to Hangzhou Jinxi Hotel.

- By airport shuttle bus: It takes about one hour to take a airport shuttle bus from airport to Hangzhou Railway Station. Take a taix when you get off the bus to Jinxi Hotel.

- By Taix: It takes about RMB 120 from airport to Jinxi Hotel.

#### 2) Arriving at the Hangzhoudong Railway Station

The map from Hangzhoudong Railway Station to Jinxi Hotel.

Upon arriving at Hangzhoudong Railway Station, we recommend you take a taxi to Jinxi Hotel.

#### 3) Arriving at the Hangzhou Railway Station

The map from Hangzhou Railway Station to Jinxi Hotel.

Upon arriving at Hangzhou Railway Station, we recommend you take a taxi to Jinxi Hotel.

#### Location

Location A: Hangzhoudong Railway Station (about 12 km to Jinxi Hotel)

Location B: Hangzhou International Airport (Xiaoshan)(about 35 km to Jinxi Hotel)

Location C: Jinxi Hotel

Location D: Hangzhou Railway Station (about 8 km to Jinxi Hotel)

Click <u>here</u> to view large map.

It's recommended that you access this website using IE7 or Firefox

Conference Admin

Powered by Duckling(CSP 1.4.8p7)

# November 16-19, 2014. Hangzhou, China The 23rd Asian Test Symposium

# **General Information**

Symposium Overview

News

Committee

Contact Us

## The Symposium

Date&Location

**VISA**

Venue

Accommodation

Registration

# Technical Program

Keynote & Invited Talks

**Tutorial**

**Advance Program**

For Speakers

For Session Chairs

Social Event

## **Submissions**

Call for Papers

Electronic Paper

**Doctoral Thesis Award**

#### Related Links

IEEE TTTC

WRTLT'14

**ATS History**

# Accommodation

# Hangzhou Jinxi Hotel(杭州金溪山庄)

| Address     | No.39 Causeway yang, Hangzhou                                                                                                                    |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| www         | http://www.jinxihotel.com/weben/Public/Default.aspx                                                                                              |  |  |

| RACATVATIAN | 1. Please fill and return the hotel reservation form (doc ) by October 15, 2014 to receive the conference discount rate. (Limited availability.) |  |  |

|             | 2. Reservation by email: <a href="mailto:ats14@ict.ac.cn">ats14@ict.ac.cn</a> .                                                                  |  |  |

| Direction   | Please check "Venue" for details.                                                                                                                |  |  |

| Room Rate   | View it in <u>JinxiHotel Reservation Form </u> Ø.                                                                                                |  |  |

| Contact     | TEL: (+86)0571-87992288-690                                                                                                                      |  |  |

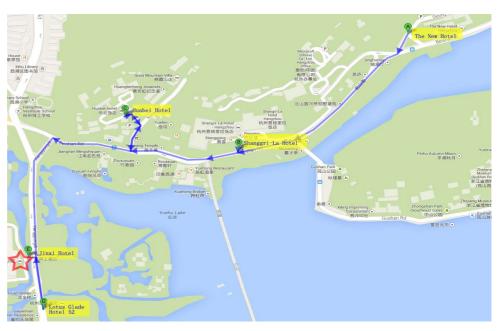

#### **Other Hotels:**

- The conference only offer hotel reservation for the ATS14 venue, Hangzhou Jinxi Hotel

- If you want to select other hotels, you can refer to the following hotels which are in walking distance to the venue.

- You should contact these hotels by yourself for reservation.

- Room rates in the following tables are just for reference. Please contact the hotel to get the exact rates for reservation.

#### Lotus Glade Hotel 52(莲遇52度假酒店)

| Address           | No. 38 Yang Gongdi , Xihu District, Hangzhou                          |

|-------------------|-----------------------------------------------------------------------|

| www               | http://www.lianyu52.com/                                              |

| Distance To Venue | 6 minutes' walk to JinxiHotel. Please view the map below for details. |

| Room Rate         | Garden View Room: RMB 768; Scenery Room RMB 818                       |

Contact TEL: (+86)0571-87999767

# Hangzhou The New Hotel (杭州新新饭店)

| Address           | No. 58 North Hill Street, Hangzhou                                     |

|-------------------|------------------------------------------------------------------------|

| www               | http://www.thenewhotel.com/Home/Index?lan=en-us                        |

| Distance To Venue | 12 minutes' walk to JinxiHotel. Please view the map below for details. |

| Room Rate         | Standard Room: RMB 686; King Room: RMB 868                             |

| Contact           | TEL: (+86)0571-87660000                                                |

# Shanggri-La Hotel (香格里拉饭店)

| Address           | No. 78 Beishan Road, Hangzhou, China                                   |

|-------------------|------------------------------------------------------------------------|

| www               | http://www.shangri-la.com/hangzhou/shangrila/                          |

| Distance To Venue | 8 minutes' walk to Jinxi Hotel. Please view the map below for details. |

| Room Rate         | Standard Room: RMB 1058                                                |

| Contact           | TEL: (+86)0571-87977951                                                |

# Huabei Hotel (华北饭店)

| Address                                                                                         | No. 18 Qixia Rideg, Hangzhou, China                   |  |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|

| www                                                                                             | http://www.hzhbfd.com/main.asp                        |  |

| Distance To Venue About 15 minutes' walk to Jinxi Hotel. Please view the map below for details. |                                                       |  |

| Room Rate                                                                                       | Standard Room: RMB 508; Deluxe Standard Room: RMB 628 |  |

| Contact                                                                                         | TEL: (+86)0571-87977951                               |  |

## Hotels Location:

Location A: Hangzhou The New Hotel

Location B: Shanggri-La Hotel

Location C: Huabei Hotel

Location D: Lotus Glade Hotel 52

Location E: Jinxi Hotel(Venue)

Click here to view large map.

It's recommended that you access this website using IE7 or Firefox

Conference Admin

# November 16-19, 2014. Hangzhou, China The 23rd Asian Test Symposium

# General Information

Symposium Overview

News

Committee

Contact Us

# The Symposium

Date&Location

**VISA**

Venue

Accommodation

Registration

# **Technical Program**

Keynote & Invited Talks

**Tutorial**

**Advance Program**

For Speakers

For Session Chairs

Social Event

#### Submissions

Call for Papers

Electronic Paper Submission

**Doctoral Thesis Award**

#### Related Links

**IEEE TTTC**

WRTLT'14

**ATS History**

# Registration

## **Symposium Registration Fees**

| ATS Registration       | Advance,Before Oct.<br>24(US\$) | Late,After Oct. 24/On<br>Site(US\$) |

|------------------------|---------------------------------|-------------------------------------|

| IEEE Member Fee        | 570.00                          | 684.00                              |

| Non-Member Fee         | 684.00                          | 821.00                              |

| Student Member Fee     | 314.00                          | 376.00                              |

| Student Non-Member Fee | 570.00                          | 684.00                              |

| IEEE Life Member Fee   | 314.00                          | 376.00                              |

A full registration is required for each accepted paper by September 15.

- Only full registration includes the social event and banquet.

- **WRTLT** and **ATS** registrations are separate. Go to the <u>WRTLT website</u> for registration information.

Invitation letter for visa application:

Please contact: ats14@ict.ac.cn, if you need an invitation letter for visa application.

#### **Tutorial Fees**

ATS 2014 features two half-day tutorials on Nov. 16, 2014.

#### TUTORIAL I:

"Test, Diagnosis, and Root-Cause Identification of Failures for Boards and Systems"

Prof. Krishnendu Chakrabarty, Dept. of Electrical and Computer Engineering, Duke University

TUTORIAL II:

"Statistical Adaptive Test Methods Targeting 'Zero Defect' IC Quality and Reliability" Prof. Adit D. Singh, Dept. of Electrical and Computer Engineering, Auburn University

| Tutorial Registration |                 | Advance,<br>Before<br>Oct.24(US\$) | Late, After Oct.<br>24/On<br>Site(US\$) |

|-----------------------|-----------------|------------------------------------|-----------------------------------------|

| Tutorial I & II       | IEEE Member Fee | 200.00                             | 240.00                                  |

|                       | Non-Member Fee  | 240.00                             | 290.00                                  |

|                       | Student Fee     | 110.00                             | 130.00                                  |

| Only Tutorial I       | IEEE Member Fee | 150.00                             | 180.00                                  |

|                       | Non-Member Fee  | 190.00                             | 220.00                                  |

|                       | Student Fee     | 80.00                              | 100.00                                  |

| Only Tutorial II | IEEE Member Fee | 150.00 | 180.00 |

|------------------|-----------------|--------|--------|

|                  | Non-Member Fee  | 190.00 | 220.00 |

|                  | Student Fee     | 80.00  | 100.00 |

#### **Extra Page Fees for Regular Papers**

- ATS'14 regular papers are allotted 6 pages free of charge. Each additional page beyond 6 pages will charge US\$ 160. A maximum of 2 additional pages is allowed.

- Pay for the extra page charges in the online registration system when you make the symposium registration.

#### **Extra Social Event Ticket**

• US\$90 per ticket

#### **Registration Cancellation Policy**

- All refunds/cancellation requests must be provided in writing and received by October 31, 2014.

- There will be an administration fee of US\$ 150 deducted from each refund.

- Please submit all requests to Shufeng Liu by e-mail (ats14@ict.ac.cn).

## Registration

- Click for online registration.

- Online registration requires major credit card account.

Please Contact <a href="mailto:ats14@ict.ac.cn">ats14@ict.ac.cn</a> if you need any assistance.

# 国内代表注册, 请点击进入

It's recommended that you access this website using IE7 or Firefox

Conference Admin

# November 16-19, 2014. Hangzhou, China The 23rd Asian Test Symposium

## General Information

Symposium Overview

News

Committee

Contact Us

#### The Symposium

Date&Location

**VISA**

Venue

Accommodation

Registration

# **Technical Program**

Keynote & Invited Talks

**Tutorial**

**Advance Program**

For Speakers

For Session Chairs

Social Event

#### Submissions

Call for Papers

Electronic Paper Submission

**Doctoral Thesis Award**

#### Related Links

**IEEE TTTC**

WRTLT'14

**ATS History**

# Keynote & Invited Talks

- · Keynote Address: Prof. Shawn Blanton, CMU

- Invited Talk I: Mr. Greg Aldrich, Mentor Graphics

- Invited Talk II: Prof. David Wei Zhang, Fudan University

# **Keynote Speaker**

#### **Prof. Shawn Blanton**

Department of Electrical and Computer Engineering

Carnegie Mellon University

**Biography:** Shawn Blanton is a professor in the Department of Electrical and Computer Engineering at Carnegie Mellon University where he serves as director of the Center for Silicon System Implementation (CSSI), an organization consisting of 18 faculty members and over 80 students focused on the design and manufacture of silicon-based systems. He received the Bachelor's degree in engineering from CalvinCollege in 1987, a Master's degree in Electrical Engineering in 1989 from the University of Arizona, and a Ph.D. degree in Computer Science and Engineering from the University of Michigan, Ann Arborin 1995.

Professor Blanton's research interests are housed in the Advanced Chip Testing Laboratory (ACTL) and include the design, verification, test and diagnosis of integrated, heterogeneous systems. He has published many papers in these areas and has several issued and pending patents in the area of IC test and diagnosis. Prof. Blanton has received the National Science Foundation Career Award for the development of a microelectromechanical systems (MEMS) testing methodology and two IBM Faculty Partnership Awards. He is a Fellow of the IEEE, and is the recipient of the 2006 Emerald Award for outstanding leadership in recruiting and mentoring minorities for advanced degrees in science and technology.

# **Invited Talk**

#### Mr. Greg Aldrich

Marketing Director at Mentor Graphics

Title: Transformation of DFT: From Load Board to Dashboard

Abstract: With the invention of scan in the late 70's, design-for-test and test generation technologies were originally relegated to a screening task for detecting manufacturing defects in processed wafers and packaged devices. Technology advances added sophisticated defect analysis capabilities, boosting the value of DFT as a critical part of yield ramp up. Today as digital electronics become more and more prevalent in safety critical functions within the automotive, aerospace, medical and similar industries, the role and value DFT plays in the design cycle and manufacturing process continues to increase and transform. In a quest to satisfy new safety standards like ISO26262 and DO-254, electronics systems manufacturers are looking for new technologies to ensure that electronic subsystems are defect free and fully functional - throughout the life of the system. Design-for-test technologies are already supporting these stringent requirements with capabilities such as built-in self-test (BIST) and power-on test. As technologies like fly-by-wire and the driverless car become reality, DFT will become an even more crucial player in support of real-time system level safety standards. The speaker will review the evolution of DFT technologies that have occurred in the past and discuss where future technologies can further expand the scope and value of DFT.

**Biography:** Greg Aldrich is the Director of Marketing for the Silicon Test Solutions product group at Mentor Graphics. Previously, Aldrich held a variety of technical and product marketing positions at Mentor Graphics. Prior to joining Mentor, Aldrich served in various engineering and marketing roles at Interconnectix (Beaverton, Oregon), Sunrise Test Systems (San Jose, California), and Amdahl Corporation (Sunnyvale, California). He holds a bachelor's degree in Electrical Engineering from the University of Illinois at Urbana-Champaign.

Qing-Qing Sun

Fudan University

Title: The Characterization Challenges in Modeling Semi-Floating Gate Transistors

**Abstract:** Semi-Floating gate transistors (SFGT) is a new type of semiconductor device with potential applications in Dynamic Read Access Memories (DRAM) and CMOS Image Sensors (CIS). The operation speed of SFGT is almost in the same level of traditional SRAM which has the operation speed below 1 ns. Although SFGT shows attractive performance due to its fast speed and low power consumption, the ERASE/READ/WRITE/READ operation of SFGT is rather complicate which introduce

many challenges in device characterizations. In this report, we will firstly talk about the operation scheme of SFGT during the READ/ERASE/WRTIE and shows the performance of the device we get with our test methodology. Secondly, we will discuss the challenges and accuracy of the test methods when device is operated at ultra-high speed.

**Biography:** Qing-Qing Sun received his Ph.D. degrees in microelectronics and solid state electronics from Fudan University, Shanghai, in 2009. He received B.S. (2004), Fudan University, in Physics. In 2009 he joined the department of microelectronics, Fudan University, as a Lecturer. He was promoted to be Associate Professor and Full Professor in 2011 and 2013, respectively. He has authored or co-authored more than 90 papers in journals and conferences and awarded more than 20 patents. His research interests include novel semiconductor devices, atomic layer deposition, resistive switching memories and advanced interconnect technology.

It's recommended that you access this website using IE7 or Firefox

Conference Admin

Powered by Duckling(CSP 1.4.8p7)

# November 16-19, 2014. Hangzhou, China The 23rd Asian Test Symposium

## General Information

Symposium Overview

News

Committee

Contact Us

## The Symposium

Date&Location

**VISA**

Venue

Accommodation

Registration

# **Technical Program**

Keynote & Invited Talks

**Tutorial**

**Advance Program**

For Speakers

For Session Chairs

Social Event

#### Submissions

Call for Papers

Electronic Paper Submission

**Doctoral Thesis Award**

#### Related Links

IEEE TTTC

WRTLT'14

**ATS History**

#### **Tutorial**

#### • TUTORIAL I:

"Test, Diagnosis, and Root-Cause Identification of Failures for Boards and Systems" Prof. Krishnendu Chakrabarty, Dept. of Electrical and Computer Engineering, Duke University

• TUTORIAL II:

"Statistical Adaptive Test Methods Targeting 'Zero Defect' IC Quality and Reliability" Prof. Adit D. Singh, Dept. of Electrical and Computer Engineering, Auburn University

| Tutorial I |                                                                                              |  |

|------------|----------------------------------------------------------------------------------------------|--|

| Title      | Test, Diagnosis, and Root-Cause Identification of Failures<br>for Boards and Systems         |  |

| Presenter  | Prof. Krishnendu Chakrabarty  Dept. of Electrical and Computer Engineering,  Duke University |  |

## **Biography**

Krishnendu Chakrabarty is the William H. Younger Distinguished Professor of Engineering in the Department of Professor of Electrical and Computer Engineering and Professor of Computer Science at Duke University. In addition, he serves as the Executive Director of Graduate Studies in Electrical and Computer Engineering. He is also a Chair Professor at Tsinghua University, Beijing, China. Prof. Chakrabarty is a recipient of the National Science Foundation Early Faculty (CAREER) award, the Office of Naval Research Young Investigator award, the Humboldt Research Award from the Alexander von Humboldt Foundation, Germany, and 10 best paper awards at major IEEE conferences. He is also a recipient of the Distinguished Alumnus Award from the Indian Institute of Technology, Kharagpur (2014).

Prof. Chakrabarty's current research projects include: testing and design-for-testability of integrated circuits; digital microfluidics, biochips, and cyberphysical systems; optimization of digital print and enterprise systems. Prof. Chakrabarty is a Fellow of ACM, a Fellow of IEEE, and a Golden Core Member of the IEEE Computer Society. He holds four US patents and he has several pending patents. He was a 2009 Invitational Fellow of the Japan Society for the Promotion of Science (JSPS). He served as a Distinguished Visitor of the IEEE Computer Society during 2005-2007 and 2010-2012, and as a Distinguished Lecturer of the IEEE Circuits and Systems Society during 2006-2007 and 2012-2013. Currently he serves as an ACM Distinguished Speaker.

Prof. Chakrabarty served as the Editor-in-Chief of IEEE Design & Test of Computers during 2010-2012. Currently he serves as the Editor-in-Chief of ACM Journal on Emerging Technologies in Computing Systems. He is also an Associate Editor of IEEE Transactions on Computers, IEEE Transactions on Biomedical Circuits and Systems, and ACM Transactions on Design Automation of Electronic Systems.

#### **Abstract**

The gap between working silicon and a working board/system is becoming more significant and problematic as technology scales and complexity grows. The result of this increasing gap is failures at the board and system level that cannot be duplicated at the component level. These failures are most often referred to as "NTFs" (No Trouble Founds). The result of these NTFs can range from higher manufacturing costs and inventories to failure to get the product out of the door. The problem will only get worse as technology scales and will be compounded as new packaging techniques (SiP, SoC, 3D) extend and expand Moore's law. This is a problem that must be solved, yet, little effort has been applied up to this point. This tutorial will provide a detailed background on the nature of this problem and will provide DFT, test, and root-cause identification solutions at the board/system level.

| Tutorial II |                                                                                      |  |  |

|-------------|--------------------------------------------------------------------------------------|--|--|

| Title       | Statistical Adaptive Test Methods Targeting 'Zero Defect' IC Quality and Reliability |  |  |

| Presenter   | Prof. Adit D. Singh  Dept. of Electrical and Computer Engineering, Auburn University |  |  |

#### **Biography**

Adit D. Singh is James B. Davis Professor of Electrical and Computer Engineering at Auburn University, where he directs the VLSI Design and Test Laboratory. His technical interests span all aspects of VLSI test and reliability. He has published nearly two hundred research papers, served as a consultant for several major semiconductor companies, and holds international patents that have been licensed to industry. He has held leadership roles at international test conferences, including serving as General Chair of the 2000 IEEE VLSI Test Symposium, the 2003 IEEE Defect Based Test Workshop, and the 2004 IEEE Memory Test Workshop. He also serves on the editorial boards of IEEE Design and Test Magazine, and JETTA. Dr. Singh is a Fellow of IEEE, a Golden Core member of the IEEE Computer Society and is past chair of the IEEE Test Technology Technical Council. He can be reached at email: adsingh@auburn.edu.

#### Abstract

Integrated circuits fabricated in aggressively scaled nanometer scale technologies are susceptible to a wide range of random manufacturing defects, some of which can be extremely difficult to reliably detect in post manufacturing testing. Meanwhile commercial applications continue to demand ever higher IC quality, most notably a "zero defect" target from automotive manufacturers. To cost effectively meet these new quality and reliability challenges, innovative new statistical screening techniques and adaptive test methodologies are being developed. These attempt to improve test effectiveness and optimize test costs by identifying "suspect" parts for more extensive testing, using tests specially targeted at the suspected failure mode. Adaptive test methods fall into two broad categories: those that exploit the statistics of defect distribution on wafers, and those that exploit the correlation in the variation of process and performance parameters on wafers. This tutorial presents test methodologies that span both these categories, and illustrates their effectiveness with results from a number of recently published experimental studies on production digital and analog circuits. Commercial tools offered by a number of new companies that have emerged in the "Adaptive Test" space will also be discussed. Broadly, these aim provide to support for the sharing and leveraging of results from the different tests in the test flow for effective test adaptation and optimization.

It's recommended that you access this website using IE7 or Firefox

Conference Admin

Powered by Duckling(CSP 1.4.8p7)

# November 16-19, 2014. Hangzhou, China The 23rd Asian Test Symposium

## General Information

Symposium Overview

News

Committee

Contact Us

# The Symposium

Date&Location

**VISA**

Venue

Accommodation

Registration

# **Technical Program**

Keynote & Invited Talks

**Tutorial**

**Advance Program**

For Speakers

For Session Chairs

Social Event

#### Submissions

Call for Papers

Electronic Paper Submission

**Doctoral Thesis Award**

#### Related Links

IEEE TTTC

WRTLT'14

**ATS History**

# ATS 2014 Advance Program

#### Nov. 16

8:30am - 12:00pm

Tutorial I: Test, Diagnosis, and Root-Cause Identification of Failures for Boards and Systems

Prof. Krishnendu Chakrabarty, Duke University

2:00pm-6:00pm

Tutorial II: Statistical Adaptive Test Methods Targeting 'Zero Defect' IC Quality and Reliability

Prof. Adit D. Singh, Auburn University

#### Nov. 17

8:30am - 9:00am

**Opening Session**

9:00am - 10:00am

Keynote: Improving Design, Manufacturing, and Even Test through Test-Data Mining Prof. Shawn Blanton, Carnegie Mellon University

10:00am - 10:30am Coffee break

10:30am - 11:15am

Invited talk I: Transformation of DFT: From Load Board to Dashboard Mr. Greg Aldrich, Marketing Director at Mentor Graphics

11:15am - 12:00pm

Invited talk II: The Characterization Challenges in Modeling Semi-Floating Gate Transistors Prof. David Wei Zhang, Fudan University

12:00pm - 1:30pm Lunch

1:30pm – 2:45pm Session 1A/1B/1C

#### **Session 1A: 3D Testing**

Session Chair: Li Jiang, Shanghai Jiao Tong University

• BIST-Assisted Tuning Scheme for Minimizing IO-Channel Power of TSV-Based 3D DRAMs

Yun-Chao Yu<sup>1</sup>, Chi-Chun Yang<sup>1</sup>, Jin-Fu Li<sup>1</sup>, Chih-Yen Lo<sup>2</sup>, Chao-Hsun Chen<sup>2</sup>, Jenn-Shiang Lai<sup>2</sup>, Ding-Ming Kwai<sup>2</sup>, Yung-Fa Chou<sup>2</sup>, and Cheng-Wen Wu<sup>3</sup>

<sup>1</sup>Department of Electrical Engineering National Central University

#### • Dual-Speed TAM Optimization of 3D SoCs for Mid-Bond and Post-Bond Testing

Kele Shen<sup>1</sup>, Dong Xiang<sup>2</sup> and Zhou Jiang<sup>2</sup>

<sup>1</sup>Department of Computer Science, Tsinghua University

#### • Optimized Pre-bond Test Methodology for Silicon Interposer Testing

Katherine Shu-Min Li<sup>1</sup>, Sying-Jyan Wang<sup>2</sup>, Jia-Lin Wu<sup>1</sup>, Cheng-You Ho<sup>1</sup>, Yingchieh Ho<sup>3</sup>, Ruei-Ting Gu<sup>1,4</sup>, Bo-Chuan Cheng<sup>4</sup>

<sup>1</sup>Department of Computer Science, National Sun Yat-sen University, Kaohsiung, Taiwan

#### Session 1B: Reliability

Session Chair: Zhiyuan Wang, Huawei Corp.

#### • Design of a Radiation Hardened Latch for Low-power Circuits

Huaguo Liang<sup>1</sup>, Zhi Wang<sup>1</sup>, Zhengfeng Huang<sup>1</sup>, and Aibin Yan<sup>2</sup>

<sup>1</sup>School of Electronic Science and Applied Physics, Hefei University of Technology, Hefei 230009, P.R. China

#### • Optimal Redundancy Designs for CNFET-Based Circuits

Da Cheng, Fangzhou Wang, Feng Gao, and Sandeep K. Gupta

Ming Hsieh Department of Electrical Engineering, University of Southern California, Los Angeles, CA,

USA

#### A Heuristically Mechanical Model for Accurate and Fast Soft Error Analysis

Jiajia Jiao, Yuzhuo Fu

School of Micro Electronics, Shanghai Jiao Tong University, Shanghai, China

#### Special Session 1C: Resilient Circuit Design and Test

#### Moderator: Mehdi Tahoori, Karlsruhe Institute of Technology, Germany

• Error Resilient Real-Time State Variable Systems for Signal Processing and Control Suvadeep Banerjee<sup>1</sup>, A´ lvaro Go´mez-Pau², Abhijit Chatterjee<sup>1</sup> and Jacob A. Abraham³

<sup>1</sup>School of Electrical and Computer Engineering, Georgia Institute of Technology

#### · Variability and Soft-Error Resilience in Dependable VLSI Platform

Yukio Mitsuyama<sup>1</sup>, and Hidetoshi Onodera<sup>2</sup>,

#### • Adaptive Mitigation of Parameter Variations

1 2 1 2

<sup>&</sup>lt;sup>2</sup>Information and Communication Research Lab. Industrial Technology Research Institute

<sup>&</sup>lt;sup>3</sup>Department of Electrical Engineering, National Tsing Hua University

<sup>&</sup>lt;sup>2</sup>School of Software, Tsinghua University

<sup>&</sup>lt;sup>2</sup>Department of Computer Science, National Chung Hsing University, Taichung, Taiwan

<sup>&</sup>lt;sup>3</sup>Department of Electrical Engineering, National Dong Hwa University, Hualien, Taiwan

<sup>&</sup>lt;sup>4</sup>Advanced Semiconductor Engineering (ASE) Group, Kaohsiung, Taiwan

<sup>&</sup>lt;sup>2</sup>School of Computer and Information, Hefei University of Technology, Hefei 230009, P.R. China

<sup>&</sup>lt;sup>2</sup>Universitat Polit`ecnica de Catalunya, Barcelona, Spain

<sup>&</sup>lt;sup>3</sup>Electrical and Computer Engineering, University of Texas at Austin

<sup>&</sup>lt;sup>1</sup>Kochi University of Technology, <sup>2</sup> Kyoto University

Farshad Firouzi , Fangming Ye , Saman Kiamehr , Krishnendu Chakrabarty , and Mehdi B. Tahooriy

<sup>1</sup>Karlsruhe Institute of Technology, Germany

2:45pm - 3:15pm Coffee break

3:15pm – 4:30pm Session 2A/2B/2C

#### Session 2A: Testing of Emerging Technologies

Session Chair: Sandeep Gupta, Univ. of Southern California

· Reliability-Driven Pipelined Scan-Like Testing of Digital Microfluidic Biochips

Zipeng Li<sup>1</sup>, Trung Anh Dinh<sup>2</sup>, Tsung-Yi Ho<sup>3</sup>, Krishnendu Chakrabarty<sup>1</sup>

<sup>1</sup>Department of Electrical and Computer Engineering, Duke University, Durham, NC, USA

<sup>2</sup>Graduate School of Information Science and Engineering, Ritsumeikan University, Shiga, Japan

<sup>3</sup>Computer Science Department, National Chiao Tung University, Hsinchu, Taiwan

A Cost-Effective Stimulus Generator for Battery Channel Characterization in Electric Vehicles

Shao-Feng Hung, Long-Yi Lin, and Hao-Chiao Hong

Department of Electrical and Computer Engineering, National Chiao Tung University, Hsinchu, Taiwan

Generator for Test Set Construction of SMGF in Reversible Circuit by Boolean Difference Method

Bappaditya Mondal<sup>1</sup>, Dipak Kumar Kole<sup>1</sup>, Debesh Kumar Das<sup>2</sup> and Hafizur Rahaman<sup>1</sup>

<sup>1</sup>Department of Information Technology, Indian Institute of Engineering Science and Technology, Shibpur, India

#### **Session 2B: SoC Testing**

Session Chair: Yu Huang, Mentor Graphics

• High-Speed Serial Embedded Deterministic Test for System-on-Chip Designs

Maciej Trawka Grzegorz Mrugalski<sup>1</sup>, Nilanjan Mukherjee<sup>1</sup>, Artur Pogiel<sup>2</sup>, Janusz Rajski<sup>2</sup> Jakub Janicki<sup>3</sup>, Jerzy Tyszer<sup>3</sup>

<sup>1</sup>Gdańsk University of Technology, 80-233 Gdańsk, Poland

<sup>2</sup>Mentor Graphics Corporation, Wilsonville, OR 97070, USA

<sup>3</sup>Poznań University of Technology, 60-965 Poznań, Poland

• A Scalable and Parallel Test Access Strategy for NoC-Based Multicore System

Taewoo Han, Inhyuk Choi, Hyunggoy Oh, Sungho Kang

Department of Electrical and Electronic Engineering, Computer systems & reliable SoC Lab., Yonsei University, Seoul, Korea

• On Covering Structural Defects in NoCs by Functional Tests

Atefe Dalirsani, Nadereh Hatami, Michael E. Imhof, Marcus Eggenberger, Gert Schley, Martin Radetzki, Hans-Joachim Wunderlich

Institute of Computer Architecture and Computer Engineering, University of Stuttgart, Germany

<sup>&</sup>lt;sup>2</sup>Department of Electrical and Computer Engineering, Duke University, Durham, NC, USA

<sup>&</sup>lt;sup>2</sup>Department of Computer Science and Engineering, Jadavpur University, Kolkata, India

#### Special Session 2C: Design, Verification and Application of IEEE 1687

Moderator: Erik Larsson, Lund University, Sweden

• Design, Verification and Application of IEEE 1687

Farrokh Ghani Zadegan<sup>1</sup>, Erik Larsson<sup>1</sup>, Artur Jutman<sup>2</sup>, Sergei Devadze<sup>2</sup>

<sup>1</sup>Lund University, Lund, Sweden

<sup>2</sup>Testonica Lab, Tallinn, Estonia

<sup>3</sup>Hochschule Hamm-Lippstadt, Hamm, Germany

4:30pm - 5:00pm Coffee break

5:00pm – 6:40pm Session 3A/3B/3C

#### Session 3A: Post-Silicon Validation

Session Chair: Michael Hsiao, Virginia Tech.

• Silicon Evaluation of Cell-Aware ATPG Tests and Small Delay Tests

Fan Yang<sup>1</sup>, Sreejit Chakravarty<sup>1</sup>, Arun Gunda<sup>1</sup>, Nicole Wu<sup>2</sup> and Jianyu Ning<sup>2</sup>

<sup>1</sup>Avago Technologies, San Jose, CA, USA

<sup>2</sup>Avago Technologies, Shanghai, China

• On Supporting Sequential Constraints for On-Chip Generation of Post-Silicon Validation Stimuli

Xiaobing Shi and Nicola Nicolici

Department of Electrical and Computer Engineering, McMaster University, Hamilton, ON, Canada

Predicting IC Defect Level using Diagnosis

Cheng Xue and R.D. (Shawn) Blanton

ECE Department, Carnegie Mellon University, Pittsburgh, PA, USA

#### **Session 3B: Testability and Test Generation**

Session Chair: Hans-Joachim Wunderlich, University of Stuttgart

Testability-Driven Fault Sampling for Deterministic Test Coverage Estimation of Large Designs

Kun-Han Tsai

Mentor Graphics Corporation, Wilsonville, OR 97070, USA

Methodology for Early RTL Testability and Coverage Analysis and Its Application to Industrial Designs

Chandan Kumar<sup>1</sup>, Fadi Maamari<sup>1</sup>, Kiran Vittal<sup>1</sup>, Wilson Pradeep<sup>2</sup>, Rajesh Tiwari<sup>2</sup>, Srivaths Ravi<sup>2</sup>

<sup>1</sup>Atrenta Inc., San Jose, U.S.A

<sup>2</sup>Texas Instruments Inc., Bengaluru, India

• Circuit Parameter Independent Test Pattern Generation for Interconnect Open Defects

Dominik Erb<sup>1</sup>, Karsten Scheibler<sup>1</sup>, Matthias Sauer<sup>1</sup>, Sudhakar M. Reddy<sup>2</sup>, Bernd Becker<sup>1</sup>

<sup>1</sup>Chair of Computer Architecture, University of Freiburg, Germany

<sup>2</sup>Dept. of ECE, University of Iowa, USA

#### Session 3C: TTTC's Doctoral Thesis Award: Asian Semi-Final

Session Chair: Jiun-Lang Huang, National Taiwan University

· Researching on the critical techniques of metamorphic testing to provide more effective test

oracle

Zhan-Wei Hui.

PLA Univ. of Science and Technology

· Yield and reliability enhancement for 3D ICs

Li Jiang,

The Chinese University of Hong Kong

An analytical model driven framework for accurate and efficient soft error analysis in processors

Jiajia Jiao,

Shanghai Jiao Tong University

Diagnosis techniques for identifying faults in digital VLSI system Subhadip Kundu,

IIT Kharagpur

• Multiple-fault-oriented fault diagnosis for digital integrated circuits Jing Ye,

Institute of Computing Technology, Chinese Academy of Sciences

Nov. 18

9:00am - 10:15am Session 4A/4B/4C

#### **Session 4A: Yield Optimization of Memory**

Session Chair: Jin-Fu Li, National Central University

Built-In Scrambling Analysis for Yield Enhancement of Embedded Memories

Shyue-Kung Lu<sup>1</sup>, Hao-Cheng Jheng<sup>1</sup>, Hao-Wei Lin<sup>1</sup>, Masaki Hashizume<sup>2</sup>, and Seiji Kajihara<sup>3</sup>

<sup>1</sup>Dept. Electrical Engineering, National Taiwan University of Science and Technology, Taipei, Taiwan

<sup>2</sup> Institute of Technology and Science, The University of Tokushima, Tokushima, Japan

<sup>3</sup>Dept. Creative Informatics, Kyushu Institute of Technology, Kyushu, Japan

Intra-Channel Reconfigurable Interface for TSV and Micro Bump Fault Tolerance in 3-D RAMs

Kuan-Te Wu<sup>1</sup>, Jin-Fu Li<sup>1</sup>, Yun-Chao Yu<sup>1</sup>, Chih-Sheng Hou<sup>1</sup>, and Chi-Chun Yang<sup>1</sup>, Ding-Ming Kwai<sup>2</sup>, Yung-Fa Chou<sup>2</sup> and Chih-Yen Lo<sup>2</sup>

<sup>1</sup>Department of Electrical Engineering, National Central University, Taoyuan, Taiwan 320

<sup>2</sup>Information and Communication Research Laboratories, Industrial Technology Research Institute, Hsinchu, Taiwan 310

SRAM array yield Estimation under spatially-correlated process variation

Jizhe Zhang and Sandeep Gupta

Department of Electrical Engineering, University of Southern California

#### Session 4B: On-Line Parameter Testing

Session Chair: Xiaoxiao Wang, Beihang University

Temperature and Voltage Estimation Using Ring-Oscillator-Based Monitor for Field Test

Yousuke Miyake<sup>1</sup>, Yasuo Sato<sup>1</sup>, Seiji Kajihara<sup>1</sup>and YukiyaMiura<sup>2</sup>

<sup>1</sup>Kyushu Institute of Technology, Iizuka, Japan

<sup>2</sup>Tokyo Metropolitan University, Tokyo, Japan

• On-Line Transition-Time Monitoring for Die-to-Die Interconnects in 3D ICs Shi-Yu Huang<sup>1</sup>, Hua-Xuan Li<sup>1</sup>, Zeng-Fu Zeng<sup>1</sup>, Kun-Han Tsai<sup>2</sup>, and Wu-Tung Cheng<sup>2</sup>

Electrical Engineering Department, National Tsing Hua University, Taiwan

<sup>2</sup>Silicon Test Solutions, Mentor Graphics

A Novel Circuit for Transition-Edge Detection: Using a Stochastic Comparator Group to Test Transition-Edge

Takahiro J. Yamaguchi<sup>1,3</sup>, James S. Tandon<sup>2,3</sup>, Satoshi Komatsu<sup>3,4</sup>, Kunihiro Asada<sup>3</sup>

<sup>1</sup>Advantest Laboratories, Ltd., Sendai, Miyagi, Japan

<sup>2</sup>Microsemi, San Jose, CA, USA

<sup>3</sup>D2T, VDEC, The University of Tokyo, Tokyo, Japan

<sup>4</sup>School of Engineering, Tokyo Denki University, Tokyo, Japan

#### Session 4C: Embedded Tutorial-Hierarchical Scan Compression 1

Yu Huang, Mentor Graphics

ZhenXin Sun, Cadence

Ang Li, Synopsys

10:15am - 10:45am Coffee break

10:45am - 12:00pm Session 5A/5B/5C

#### Session 5A: Power/Temperature-Aware Testing

Session Chair: Seiji Kajihara, Kyushu Institute of Technology

Low Power Test Compression with Programmable Broadcast-Based Control

Sylwester Milewski<sup>1</sup>, Grzegorz Mrugalski<sup>2</sup>, Janusz Rajski<sup>2</sup>, Jerzy Tyszer<sup>1</sup>

<sup>1</sup>Poznań University of Technology, 60-965 Poznań, Poland

<sup>2</sup>Mentor Graphics Corporation, Wilsonville, OR 97070, USA

• Exploit Dynamic Voltage and Frequency Scaling for SoC Test Scheduling under Thermal Constraints

Li Ling, Jianhui Jiang

School of Software Engineering, Tongji University, Shanghai, China

· High Quality Testing of Grid Style Power Gating

Vasileios Tenentes<sup>1</sup>, Saqib Khursheed<sup>2</sup>, Bashir M. Al-Hashimi<sup>1</sup>, Shida Zhong<sup>1</sup>, Sheng Yang<sup>1</sup>

<sup>1</sup>ECS, University of Southampton, UK.

<sup>2</sup>Electrical Engineering & Electronics, University of Liverpool, UK.

#### Session 5B: Trojan/Fault Detection with High Resolution

Session Chair: Katherine Shu-Min Li, National Sun Yat-Sen University

• A Resizing Method to Minimize Effects of Hardware Trojans

Byeongju Cha and Sandeep K. Gupta

Ming Hsieh Department of Electrical Engineering, University of Southern California Los Angeles, USA

High Resolution Pulse Propagation Driven Trojan Detection In Digital Logic: Optimization Algorithms and Infrastructure Sabyasachi Deyati<sup>1</sup> ,Barry John Muldrey<sup>1</sup>, Adit Singh<sup>2</sup>, Abhijit Chatterjee<sup>1</sup>

<sup>1</sup>Electrical & Computer Engineering, Georgia Institute of Technology, Atlanta GA 30332, USA

<sup>2</sup>Department of Electrical Engineering, Auburn University, AL 36849, USA

• Physically-Aware Diagnostic Resolution

John A. Porche, R. D. (Shawn) Blanton

Dept. of ECE Carnegie Mellon University Pittsburgh, PA 15213

#### Session 5C: Embedded Tutorial-Hierarchical Scan Compression 2

Yu Huang, Mentor Graphics

ZhenXin Sun, Cadence

Ang Li, Synopsys

12:00pm - 1:30pm Lunch

1:30pm - 3:10pm Session 6A/6B/6C

#### Session 6A: Analog/Memory Testing

Session Chair: Jiun-Lang Huang, National Taiwan University

• On-chip implementation of an Integrator-Based servo-loop for ADC static linearity test

Guillaume Renaud<sup>1</sup>, Manuel J. Barragan<sup>1</sup>, and Salvador Mir<sup>1</sup>, Marc Sabut<sup>2</sup>

<sup>1</sup>Universite Grenoble Alpes, TIMA, F-38000 Grenoble, France CNRS, TIMA, F-38000 Grenoble, France

<sup>2</sup>STMicroelectronics Grenoble 12, Rue Jules Horowitz, F-38000 Grenoble, France

• An ATE Based 32 Gbaud PAM-4 At-Speed Characterization and Testing Solution

Jose Moreira<sup>1</sup>, Hubert Werkmann<sup>1</sup>, Masahiro Ishida<sup>1</sup>, Bernhard Roth<sup>1</sup>, Volker Filsinger<sup>2</sup>, Sui-Xia Yang<sup>1</sup>

Advantest

<sup>2</sup>SHF Communication Technologies

· Testing of Non-Volatile Logic-Based System Chips

Yong-Xiao Chen and Jin-Fu Li Advanced Reliable Systems (ARES) Lab, Department of Electrical Engineering, National Central University, Jhongli, Taiwan 320

• Dual-Purpose Mixed-Level Test Generation Using Swarm Intelligence

Kelson Gent and Michael S. Hsiao

Bradley Department of Electrical and Computer Engineering Virginia Tech, Blacksburg, VA 24061, USA

#### Panel Session 6B: Big Data for Test

Moderators: K.-T. Tim Cheng, University of California, Santa Barbara

Harry H. Chen, MediaTek Inc.

- Learning from Production Test Data: Correlation Exploration and Feature Engineering

*Fan Lin, Chun-Kai Hsu, and Kwang-Ting Cheng Department of Electrical and Computer Engineering, University of California, Santa Barbara, CA 93106*

- Leveraging Big Data Analytics to Drive Failure Analysis in Manufacturing Operations

*David Park*,

*Optimal+*

- Data Driven Design Centric Yield Learning John Kim, Synopsys

• Perspectives on Test Data Mining from Industrial Experience Harry H. Chen,

Design Technology Department, MediaTek Inc. Hsinchu, Taiwan

# Special Session 6C: In-Field Techniques for Performance Adaption, Test, and Power-Noise Diagnosis

Moderator: Xiaoqing Wen, Kyushu Institute of Technology, Japan

Opportunities and Verification Challenges of Run-time Performance Adaptation

*Masanori Hashimoto*

Dept. Information Systems Engineering, Osaka University

• An On-Chip Digital Environment Monitor for Field Test Seiji Kajihara, Yousuke Miyake, Yasuo Sato, Yukiya Miura Kyushu Institute of Technology

On-Chip Monitoring for In-Place Diagnosis of Undesired Power Domain Problems in IC Chips

Makoto Nagata, Daisuke Fujimoto, Noriyuki Miura Graduate School of System Informatics, Kobe University, Japan

3:30pm - 10:00pm Social Event & Banquet

#### Nov. 19

9:00am - 10:15am Session 7A/7B/7C

#### **Session 7A: Timing Variation Detection**

Session Chair: Shi-Yu Huang, National Tsinghua University

• An On-Line Timing Error Detection Method for Silicon Debug

Yun Cheng<sup>1,2</sup>, Huawei Li<sup>1</sup>, Xiaowei Li<sup>1</sup>

<sup>1</sup>State Key Laboratory of Computer Architecture, Institute of Computing Technology, Chinese Academy of Sciences, Beijing, China

<sup>2</sup>University of Chinese Academy of Sciences, Beijing, China

An All Digital Distributed Sensor Network Based Framework for Continuous Noise Monitoring and Timing Failure Analysis in SoCs

Mehdi Sadi  $^I$ , Zoe Conroy  $^2$ , Bill Eklow  $^2$ , Matthias Kamm  $^2$ , Nematollah Bidokhti  $^2$  and Mark (Mohammad) Tehranipoor  $^I$

<sup>1</sup>Dept. of Electrical & Computer Engineering, University of Connecticut, Storrs, USA

<sup>2</sup>Cisco Systems, San Jose, CA, USA

• On-Chip Delay Sensor for Environments with large Temperature Fluctuations

Jibing Qiu, Guihai Yan, Xiaowei Li

State Key Laboratory of Computer Architecture, Institute of Computing Technology, Chinese Academy of Sciences, Beijing, China

## Session 7B: Delay Testing

Session Chair: Bernd Becker, University of Freiburg

Timing Evaluation Tests for Scan Enable Signals with Application to TDF Testing Jie Zou, Chao Han and Adit D. Singh Department of Electrical and Computer Engineering, Auburn University, Auburn AL, 36849 • FPGA-Based Subset Sum Delay Lines

Chung-Yun Wang<sup>1</sup>, Yu-Yi Chen<sup>1</sup>, Jiun-Lang Huang<sup>1</sup>, Xuan-Lun Huang<sup>2</sup>

<sup>1</sup>Graduate Institute of Electronics Engineering, Department of Electrical Engineering, National Taiwan University

Parallel Path Delay Fault Simulation for Multi/Many-Core Processors with SIMD Units

Yussuf Ali<sup>1</sup> Yuta Yamato<sup>1</sup> Tomokazu Yoneda<sup>1</sup> Kazumi Hatayama<sup>2</sup> Michiko Inoue<sup>1</sup>

<sup>1</sup> Nara Institute of Science and Technology, Nara, Japan

#### Special Session 7C: High Quality System Level Test and Diagnosis

Moderator: Hans-Joachim Wunderlich, University of Stuttgart

· High Quality System Level Test and Diagnosis

Artur Jutman<sup>1</sup>, Matteo Sonza Reorda<sup>2</sup>, Hans-Joachim Wunderlich<sup>3</sup>

<sup>1</sup>Testonica Lab, Tallinn, Estonia, <sup>2</sup>Politecnico di Torino, Italy, <sup>3</sup>University of Stuttgart, Germany

10:15am - 10:45am Coffee break

10:45am - 12:00pm Session 8A/8B/8C

#### Session 8A: Diagnosis

Session Chair: Sybille Hellebrand, University of Paderborn

An Efficient Diagnosis Pattern Generation Procedure to Distinguish Stuck-at Faults and Bridging Faults

Cheng-Hung Wu and Kuen-Jong Lee

Dept. of EE, National Cheng Kung University, Taiwan

• On the Generation of Diagnostic Test Set for Intra-cell Defects

Z. Sun<sup>1</sup>, A. Bosio<sup>1</sup>, L. Dilillo<sup>1</sup>, P. Girard<sup>1</sup>, A. Virazel<sup>1</sup>, E. Auvray<sup>2</sup>

<sup>1</sup>LIRMM UM2-CNRS, Montpellier, France

<sup>2</sup>ST Microelectronics, Grenoble, France

• Diagnosing Cell Internal Defects Using Analog Simulation-based Fault Models

Huaxing Tang<sup>1</sup>, Brady Benware<sup>1</sup>, Michael Reese<sup>2</sup>, Joseph Caroselli<sup>2</sup>, Thomas Herrmann<sup>3</sup>,

Friedrich Hapke<sup>4</sup>, Robert Tao<sup>2</sup>, Wu-Tung Cheng<sup>1</sup>, Manish Sharma<sup>1</sup>

<sup>1</sup>Mentor Graphics, Wilsonville, Oregon, USA

<sup>2</sup>AMD, Inc. Austin, Texas, USA

<sup>3</sup>GLOBALFOUNDRIES, Dresden, Germany

<sup>4</sup>Mentor Graphics, Hamburg, Germany

#### **Session 8B: Test Compression**

Session Chair: Huaguo Liang, Hefei University of Technology

• Improving Output Compaction Efficiency with High Observability Scan Chains

Sying-Jyan Wang<sup>1</sup>, Che-Wei Kao<sup>1</sup>, Katherine Shu-Min Li<sup>2</sup>

<sup>1</sup>Department of Computer Science and Engineering, National Chung Hsing University, Taichung, Taiwan

<sup>2</sup>Department of Computer Science and Engineering, National Sun Yat-sen University, Kaohsiung, Taiwan

• Two-Step Dynamic Encoding for Linear Decompressors

Emil Gizdarski

Synopsys Inc., 700 East Middlefield Road, Mountain View, CA 94043

<sup>&</sup>lt;sup>2</sup>Industrial Technology Research Institute, Hsinchu, Taiwan

<sup>&</sup>lt;sup>2</sup>Gunma University, Gunma, Japan

• A Case Study on Implementing Compressed DFT Architecture

A. Chandra, S. Chebiyam, and R. Kapur

Synopsys, Inc., 700 E. Middlefield Rd., Mountain View, CA, 94043, USA

#### **Special Session 8C: Hardware Security**

Moderator: Yier Jin, University of Central Florida

Leveraging Emerging Technology for Hardware Security - Case Study on Silicon Nanowire FETs and Graphene SymFETs

Yu Bi<sup>1</sup>, Pierre-Emmanuel Gaillardon<sup>2</sup>, X. Sharon Huz<sup>3</sup>, Michael Niemierz<sup>3</sup>, Jiann-Shiun Yuan<sup>1</sup>, and Yier Jin<sup>1</sup>

<sup>1</sup>Department of Electrical Engineering and Computer Science, University of Central Florida

<sup>2</sup>Ecole Polytechnique F 'ed' erale de Lausanne (EPFL) - Switzerland '

<sup>3</sup>Department of Computer Science and Engineering, University of Notre Dame

· Advanced Analysis of Cell Stability for Reliable SRAM PUFs

Alison Hosey, Md. Tauhidur Rahman, Kan Xiao, Domenic Forte, and Mohammad Tehranipoor ECE Department, University of Connecticut

• On the Use of Scan Chain to Improve Physical Attacks

Junfeng Fan<sup>1</sup>, Hua Xie<sup>2</sup>, Yiwei Zhang<sup>2</sup>

<sup>1</sup>Nationz technologies and Open Security Research, Shenzhen, China

<sup>2</sup>Nationz technologies, Shenzhen, China

It's recommended that you access this website using IE7 or Firefox

Conference Admin

# November 16-19, 2014. Hangzhou, China The 23rd Asian Test Symposium

# General Information

Symposium Overview

News

Committee

Contact Us

# The Symposium

Date&Location

**VISA**

Venue

Accommodation

Registration

# **Technical Program**

Keynote & Invited Talks

**Tutorial**

**Advance Program**

For Speakers

For Session Chairs

Social Event

#### Submissions

Call for Papers

Electronic Paper Submission

**Doctoral Thesis Award**

#### Related Links

IEEE TTTC

WRTLT'14

**ATS History**

# INSTRUCTIONS FOR SPEAKERS OF REGULAR SESSIONS/SPECIAL SESSIONS/EMBEDDED TUTORIAL

This page provides instructions for speakers of regular papers/special sessions/embedded tutorial. Panel speakers should contact their session organizers and/or moderators for further information.

#### Presentation Time:

#### Regular Paper/Special Sessions/Embedded Tutorial:

- Your paper is allotted 25 minutes as follows:

- (i) 2 minutes for introduction, set up etc.

- (ii) 20 minutes for presentation, and

- (iii) 3 minutes for Q&A.

#### Presentation Preparation Guide:

- October 31 is the deadline to submit your presentation file and related information to the ATS 2014 system. http://www.carch.ac.cn/ats2014/submitSlides/

- Only PowerPoint files are accepted, which will be played on Microsoft Windows XP.

- Focus on pertinent information

- DO NOT attempt to fit entire paper onto slides

- List only the key innovations and novel approaches on slides

- Get straight to the point, audience comprises of technical experts

- Details of proofs, previous works, and theories are redundant

- High contrast: Light lettering/lines on a dark background

- Foreground: White, yellow, light cyan

- Background: Black, dark blue, brown, dark green

- Caution: Red, orange or blue lettering and lines become unreadable when projected

- Short phrases, not long sentences: 36 point titles and 28 point text recomended

- Use large font sizes. 24 point and higher for regular text and 20 point for descriptive text.

- Use graphs instead of tables

- Use the width to height aspect ratio of most graphics displays is 4:3.

- Your company name and/or logo are only allowed to appear on the title page. Also minimize the use of product trademarks.

- Do not use any sound effects.

- Spell check your slides!

#### At the Symposium:

- Meet with your Session Chair prior to your session. You can find out the name of your Session Chair in the ATS 2014 program booklet.

- Go through the exercise of familiarizing yourself with the audio-visual equipment prior to your session.

- If, for some reason, you are unable to contact your Session Chair, please contact the registration desk as soon as possible.

#### At your Session:

- Please be present in your session at least 15 minutes before the session starts.

- Test out your presentation on the symposium PC to make sure it works as expected.

- As a courtesy to other presenters and to the attendees, follow the time guidelines very

closely. The Session Chair will give you a first reminder after 10 minutes have elapsed

and a second reminder when only 2 minutes are left. Please use these reminders to

pace your presentation appropriately, and ensure that you finish in the allotted 15/20

minutes.

- If there is any question that you do not understand, please ask the questioner or Session Chair to repeat or clarify. Lengthy discussions can be taken offline.

It's recommended that you access this website using IE7 or Firefox

Conference Admin

### November 16-19, 2014. Hangzhou, China The 23rd Asian Test Symposium

#### General Information

Symposium Overview

News

Committee

Contact Us

#### The Symposium

Date&Location

**VISA**

Venue

Accommodation

Registration

#### **Technical Program**

Keynote & Invited Talks

**Tutorial**

Advance Program

For Speakers

For Session Chairs

Social Event

#### Submissions

Call for Papers

Electronic Paper Submission

**Doctoral Thesis Award**

#### Related Links

**IEEE TTTC**

WRTLT'14

**ATS History**

#### INSTRUCTIONS TO SESSION CHAIRS

Thank you for your important contribution to ATS 2014. As "conductors" of the program, Session Chairs play an important role in ensuring that the sessions proceed in a smooth, timely, and interactive manner.

#### Time Limits:

Regular Session/Special Session/Embedded Tutorial: 25 minutes to be divided as follows:

- (i) 2 minutes for introduction, set up etc.,

- (ii) 20 minutes for presentation, and

- (iii) 3 minutes for O&A.

- Please ensure that the time limits are adhered to very strictly.

- Please give the authors two warnings during their presentation: (i) at the end of 10 minutes, and (ii) 2 minutes before the end of the presentation.

#### General Duties:

- The Session Chair will introduce the speakers, keep the time, and moderate the Q&A process.

- The Session Chair will assist the speakers with the audio-visual equipment, room lighting during the presentation, and get help from the A/V technicians in case it is needed.

#### **Pre-Session Tasks:**

- Depending on the timing of your session, you will meet with the presenters 15 minutes before the session starts.

- Report any missing speakers to the session room assistant as soon as possible.

- Please discuss with the authors the time limits for the papers. Inform them as to how you will

communicate with them the progress of time. Stress the fact that time limits will be strictly

adhered to.

#### For Each Speaker:

- Introduce the speaker.

- Keep track of time and give the speaker appropriate signals to alert the speaker.

#### Moderate the discussion by

- Reminding the audience to identify themselves and state their affiliations when asking a question.

- Clarifying questions if needed.

- Avoiding long discussions and suggesting that they be taken off-line

- Preventing any one individual from dominating the discussion

- · Asking, if needed, a few questions of your own.

It's recommended that you access this website using IE7 or Firefox

Conference Admin

## November 16-19, 2014. Hangzhou, China The 23rd Asian Test Symposium

#### **General Information**

Symposium Overview

News

Committee

Contact Us

#### The Symposium

Date&Location

**VISA**

Venue

Accommodation

Registration

#### Technical Program

Keynote & Invited Talks

**Tutorial**

Advance Program

For Speakers

For Session Chairs

Social Event

#### **Submissions**

Call for Papers

Electronic Paper Submission

**Doctoral Thesis Award**

#### Related Links

**IEEE TTTC**

WRTLT'14

**ATS History**

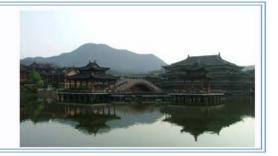

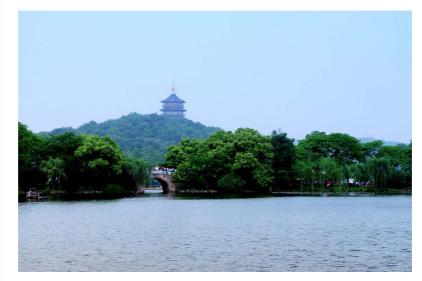

ATS'14 Social event

Time: 3:30pm-10pm, Nov. 18

#### 3:30pm A trip around the West Lake

Route of the trip: JinXi (金溪) – Quyuan Garden (曲院风荷) – Spring Dwan at Su Causeway (苏堤春晓) – Lingering Snow on the Broken Bridge (断桥残雪) – Louwailou (楼外楼)

6:00pm Banquet at the Hangzhou Louwailou restaurant

7:30pm A famous program played right on the West Lake: Impression of West Lake

#### Introductions

Introduction of Hangzhou, China

http://www.hicenter.cn/

Introduction of West Lake

http://www.answers.com/topic/west-lake

• Introduction of the program: Impression of West Lake

Strong history and culture to the West Lake and the beautiful natural scenery as a source of creativity, in-depth digging Hangzhou, an ancient folk tales, myths, cultural and historical representation of the elements of the West Lake to reproduce the same time, re-use of high-tech way, "West Lake Rain", from a side of West Lake and West Lake in the rain to reflect the natural charm of the rain. The entire landscape virtual performances, through dynamic interpretation, realistic reproduction of the Hangzhou City connotation and condensed into a natural landscape to a high standard of art in the world, introduced to the world.

It's recommended that you access this website using IE7 or Firefox

Conference Admin

### November 16-19, 2014. Hangzhou, China The 23rd Asian Test Symposium

#### **General Information**

Symposium Overview

News

Committee

Contact Us

#### The Symposium

Date&Location

**VISA**

Venue

Accommodation

Registration

#### **Technical Program**

Keynote & Invited Talks

**Tutorial**

Advance Program

For Speakers

For Session Chairs

Social Event

#### Submissions

Call for Papers

Electronic Paper Submission

**Doctoral Thesis Award**

#### Related Links

**IEEE TTTC**

WRTLT'14

**ATS History**

#### Call for Papers (pdf ∅)

The Asian Test Symposium (ATS) provides an open forum for researchers and industrial practitioners from all countries of the world, especially from Asia, to exchange innovative ideas on system, board, and device testing with design, manufacturing and field consideration in mind.

#### Scope

Original papers on, but not limited to, the following areas are invited.

- Automatic Test Pattern Generation

- Fault Modeling and Simulation

- Design Verification and Validation

- · Diagnosis and Debug

- Board and System Test

- Analog/Mixed-Signal Test

- High-Speed I/O Test

- RF Test

- Delay and Performance Test

- Memory Test/FPGA Test

- System-in-Package/3D Test

- Software Testing

- · Boundary Scan Test

- · Built-In Self-Test

- · Design-for-Testability

- · Test Compression

- · On-Line Test

- Temperature/Power-Aware Testing

- Defect-Based Testing

- Fault Tolerance

- Dependable System

- · Yield Analysis and Enhancement

- · Test Quality

- Economics of Test

- Hardware Security

#### **Submissions**

**Regular Sessions:** The ATS'14 Program Committee invites original, unpublished paper submissions on the above topics. Paper submissions should be complete manuscripts, not exceeding six pages (including figures, tables, and bibliography) in a standard IEEE two-column format. The submission will be considered evidence that upon acceptance the author(s) will submit a final camera-ready version of the paper for inclusion in the proceedings, and will present the paper at the symposium. The registration of at least one author is required for publication.

ATS'14 will present a Best Paper Award to a selected paper of exceptional quality.

The evaluation will be conducted by an award committee constituted by experts covering all aspects of test technology, based on the criteria of innovation, potential impact, and presentation quality.

#### **Key Dates**

- Submission deadline:

- May 16, 2014 May 23(extended)

- Notification of acceptance:

- Aug. 10, 2014

.

Camera ready manuscript: Sept. 5, 2014

Diamond Supporter: Silver Supporter:

Sponsored by:

It's recommended that you access this website using IE7 or Firefox

Conference Admin

Powered by Duckling(CSP 1.4.8p7)

### November 16-19, 2014. Hangzhou, China The 23rd Asian Test Symposium

#### General Information

Symposium Overview

News

Committee

Contact Us

#### The Symposium

Date&Location

**VISA**

Venue

Accommodation

Registration

#### **Technical Program**

Keynote & Invited Talks

**Tutorial**

Advance Program

For Speakers

For Session Chairs

Social Event

#### Submissions

Call for Papers

Electronic Paper Submission

**Doctoral Thesis Award**

#### Related Links

IEEE TTTC

WRTLT'14

**ATS History**

#### **Authors and Reviewers Login**

Click <u>here</u> to access the submission and peer-review system.

#### **Paper Submission**

The ATS Program Committee invites **original, unpublished paper submissions** for ATS 2014. Paper submissions should be complete manuscripts, up to six pages (inclusive of figures, tables, and bibliography) in a standard IEEE two-column format. Authors should clearly explain the significance of the work, highlight novel features, and describe its current status.